**ARISTOTLE UNIVERSITY OF THESSALONIKI

FACULTY OF SCIENCES - SCHOOL OF PHYSICS

MSc ELECTRONIC PHYSICS – RADIODETECTROLOGY**

**Pixel Design

for AMOLED Displays**

**VOSNIADIS PANAGIOTIS**

**Registration Number: 11244**

**Supervisors:**

**Siskos Stylianos, Professor**

**Pappas Ilias**

**THESSALONIKI**

**2017**

**ARISTOTLE UNIVERSITY OF THESSALONIKI

FACULTY OF SCIENCES - SCHOOL OF PHYSICS

MSc ELECTRONIC PHYSICS – RADIODETECTROLOGY**

**Pixel Design

for AMOLED Displays**

**VOSNIADIS PANAGIOTIS**

**Registration Number: 11244**

**Supervisors:**

**Siskos Stylianos, Professor**

**Pappas Ilias**

**THESSALONIKI**

**2017**

## **ACKNOWLEDGMENT**

The past two years I have had the chance to participate in the postgraduate program “Electronic Physics – Radioelectronics” of the Department of Physics of the Aristotle University of Thessaloniki. During these years I have broadened and deepened my knowledge in electronics and Telecommunications.

I would like to thank all the participants of the postgraduate program, for the knowledge, the experience and insight I gained.

Most of all, I would like to thank my supervisors, professors Stylianos Siskos and Ilias Pappas, for their guidance and support in each step of this work.

Finally, I am especially thankful to everyone who supported me during this path.

## ABSTRACT – OUTLINE

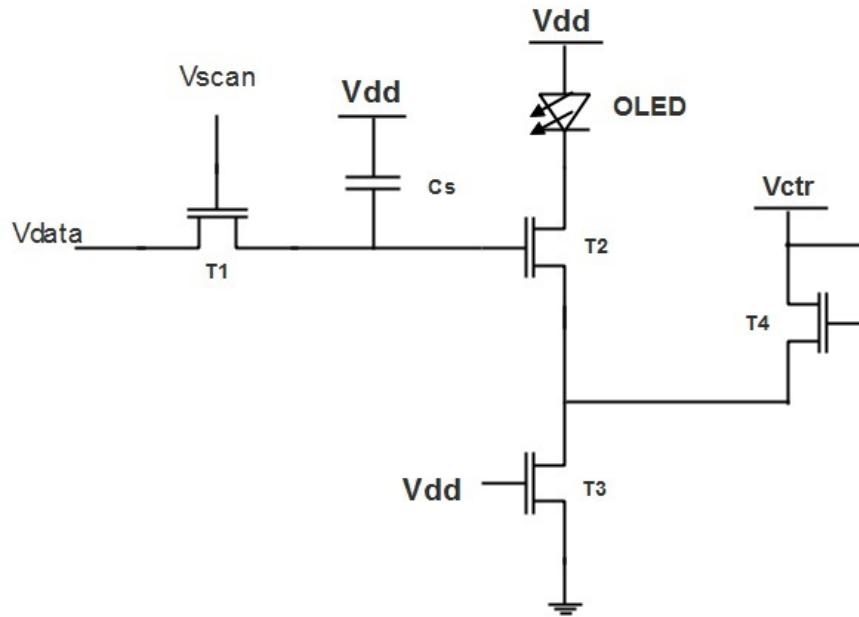

The main subject of this thesis is to develop a voltage programmable pixel circuit with a new threshold-voltage compensation technique for AMOLED displays. One of the advantages of this proposed pixel design is the simplicity of the circuit raising from the fact that requires only four TFTs and one capacitor.

Our final results for the voltage threshold variations have been confirmed by simulations. The main advantage of the proposed pixel design is that the current of the OLED is independent of the threshold voltage of the driving TFT and well controlled. Also, the threshold voltage compensation technique is implementing with a static circuit, resulting to fast response time, similar to the conventional 2T1C response time which is the fastest circuit.

The simulations for the pixel were made with *virtuoso cadence suite* and we used two TFTs models, a Low-Temperature Polycrystalline Silicon (LTPS) model and a Indium Gallium Zinc Oxide (IGZO) model.

In the first chapter the Thin-Film Transistor (TFTs) technology is presented as the most dominant technology in the area of displays. Initially an introduction to the TFTs is made, with references to the importance of the displays that use TFTs, as well as how they operate, the operation regions and the reasons why they are needed in the displays design. Subsequently, an analysis of the structure of TFTs is exhibited and the evolution of TFTs is described through a short historical review. That leads to an analysis of different kinds of the TFTs technology. Specifically, the improvement of the TFT devices characteristics, as well as the fabrication process used in the flat panel display industry. Finally, examples of Si models including amorphous silicon (a-Si), low-temperature polycrystalline silicon (LTPS) and indium gallium zinc oxide (IGZO) are listed and their advantages and disadvantages are compared to each other.

In the second chapter different types of screens like CRT-LCD-OLED are presented along with a short historical review. Additionally, a description of the basic display features of every screen is listed, as well as a comparison between them. The operation of OLED model is described and the advantages and disadvantages of LCD and OLED displays are elaborated. Furthermore, in this chapter the addressing methods in the display technology are presented. These

addressing methods have to do with the way the pixel is designed and there is a description of the three types of addressing methods: the direct method (direct), the passive matrix (PM) and the active matrix (AM). A comparison of the two basic addressing methods, the active and the passive, is also made. Finally, the architecture of the active addressing method is further described, as it is the most common method in current displays.

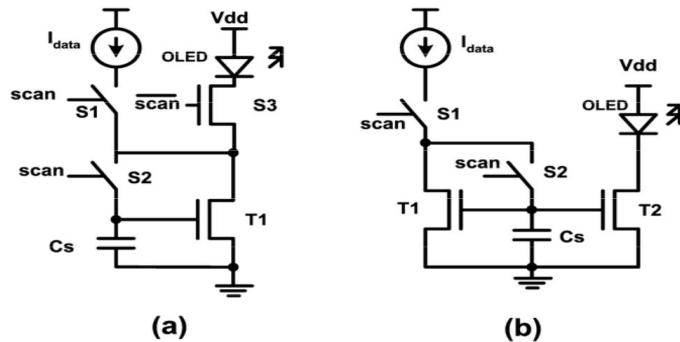

The third chapter is an analysis of the operation of the Organic Light Emitting Diode (OLED), which provided with a better solution to the design of the display's pixels for thinner high-performance displays and lower power consumption. Latest generation displays are developed by applying active addressing method technique (AMOLED). So, an introduction of different types of OLED is made. There is a description of the two different types of OLED, first with colored pixel and second with white pixel and colored filter above for the color production, and there is also a subsequent comparison of these two categories. Furthermore, an analysis of the two ways of pixel programming is provided, with voltage or with current, along with a comparison between the two and aiming to reveal their advantages and disadvantages. This chapter ends by describing the way that the conventional and simpler voltage programming pixel circuit 2T1C operates.

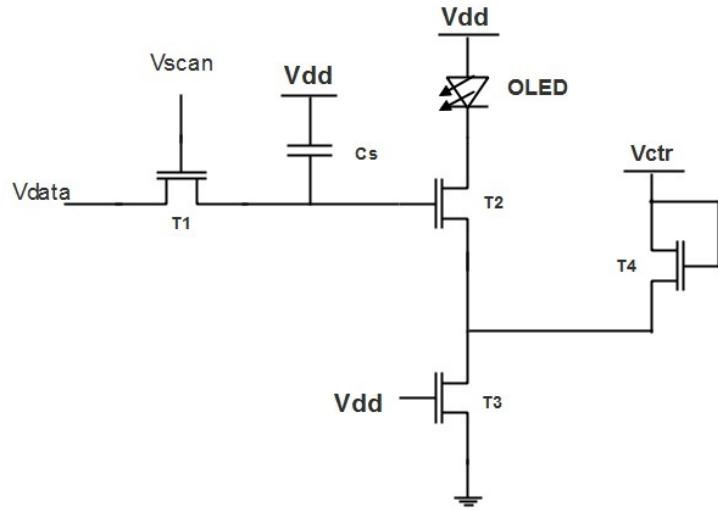

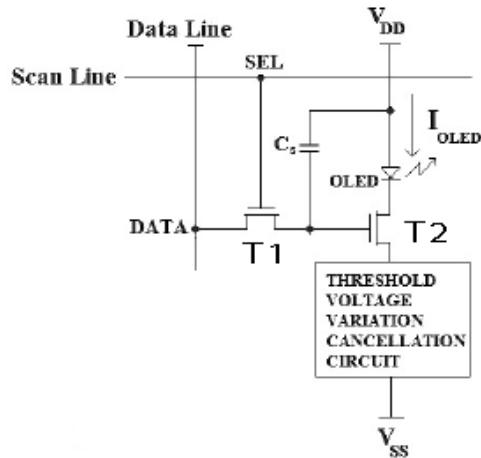

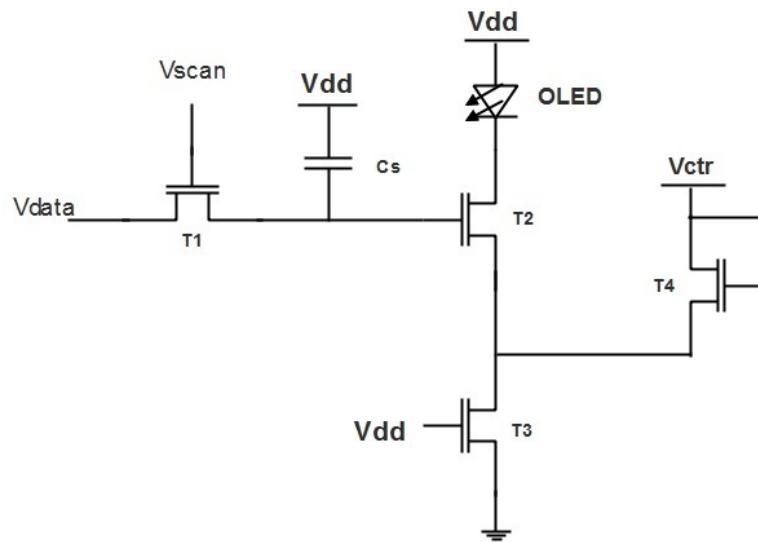

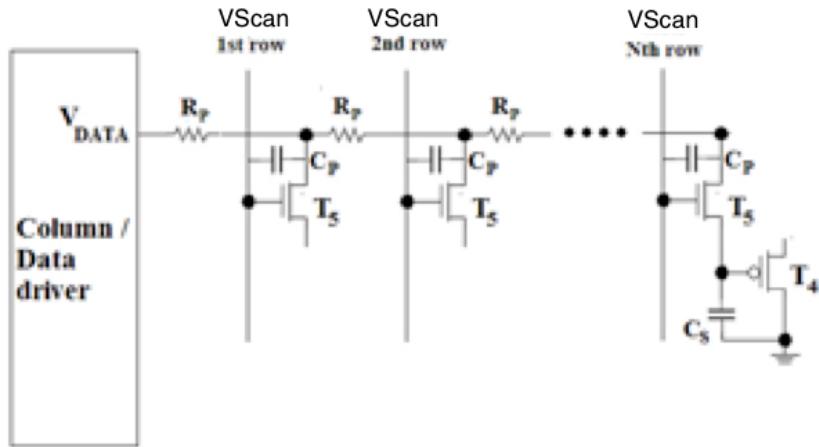

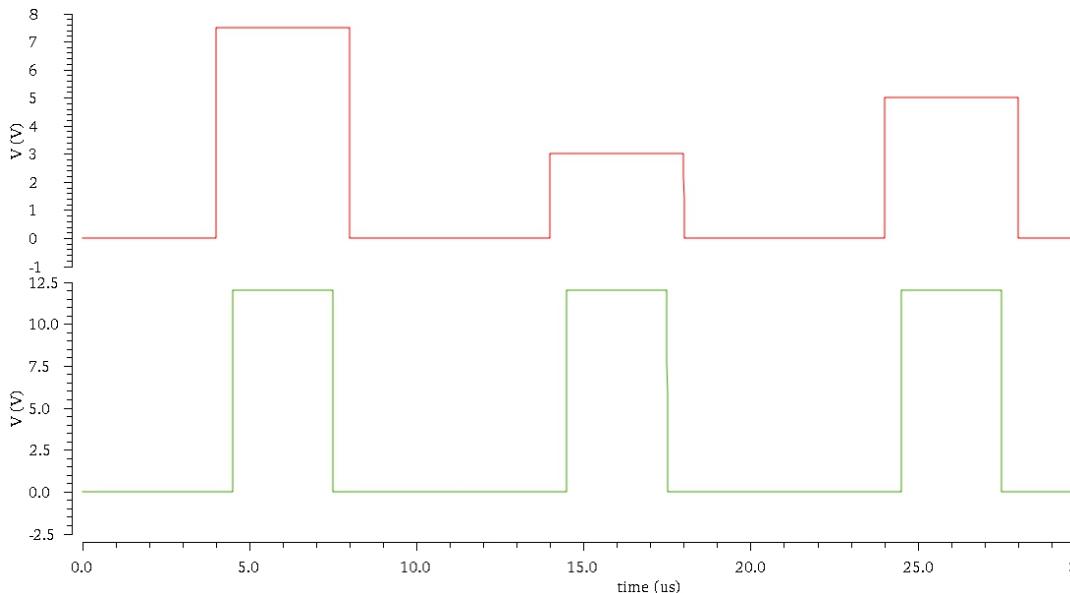

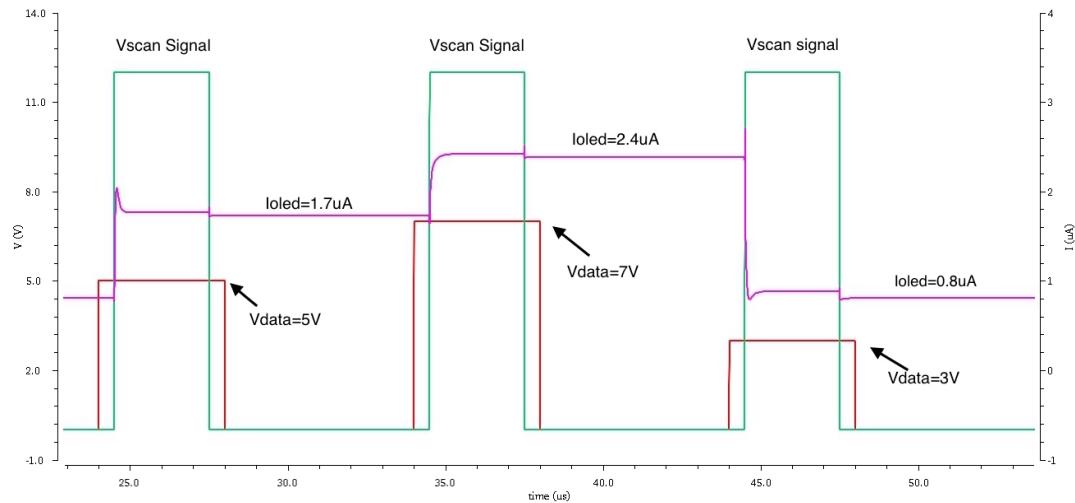

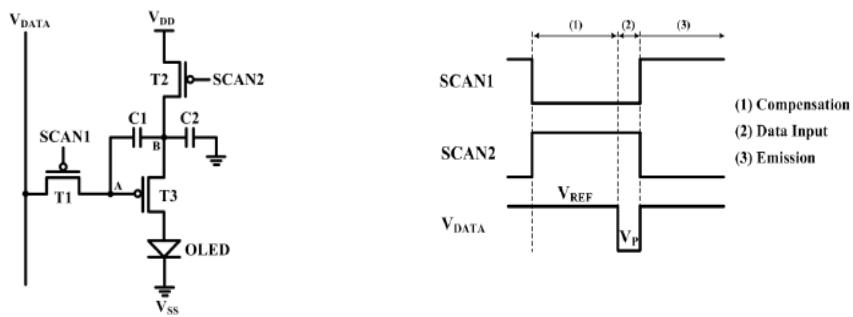

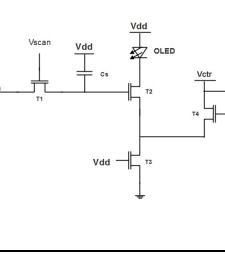

In the fourth chapter there is a step-by-step description of proposed circuit development. The circuit of the project is a voltage programmed pixel (VPPC) that has some modification of the conventional voltage programmed pixel circuit (2T1C -2TFT and 1Capacitor). As indicated, the new circuit has a new threshold-voltage compensation technique applied on the conventional 2T1C. Subsequently, the operation of the circuit is thoroughly analyzed, as well as the design specifications. The time response analysis of the circuit with the parasitic capacitance and resistances is also mentioned. We analyzed the two main signals, the Vdata and the Vscan pulse, as well as the way these two pulse results to the production of the Ioled.

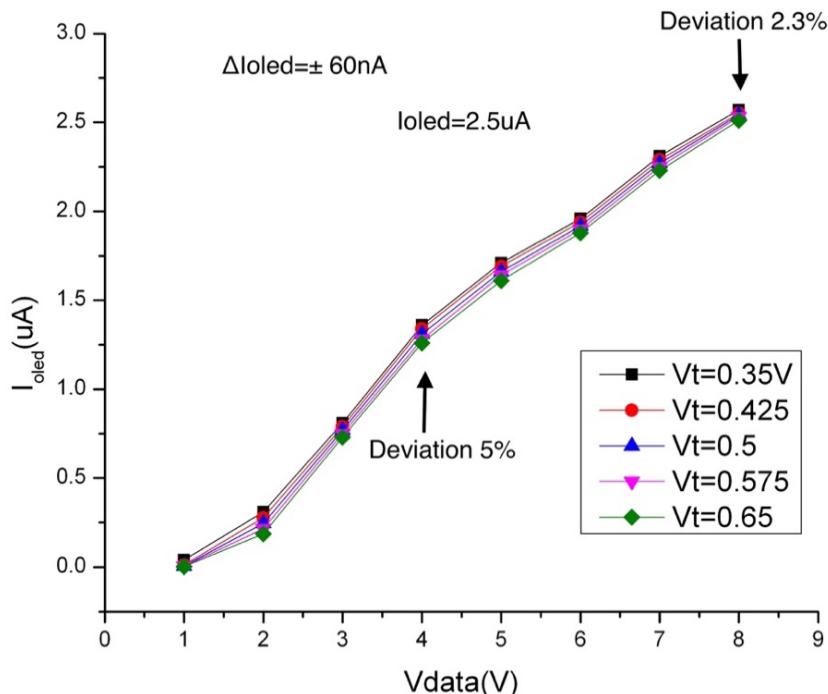

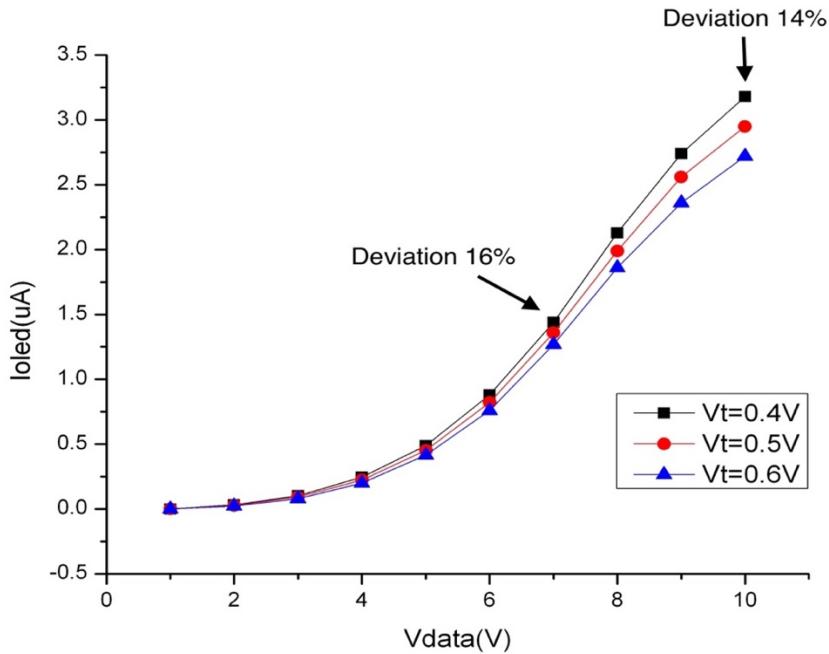

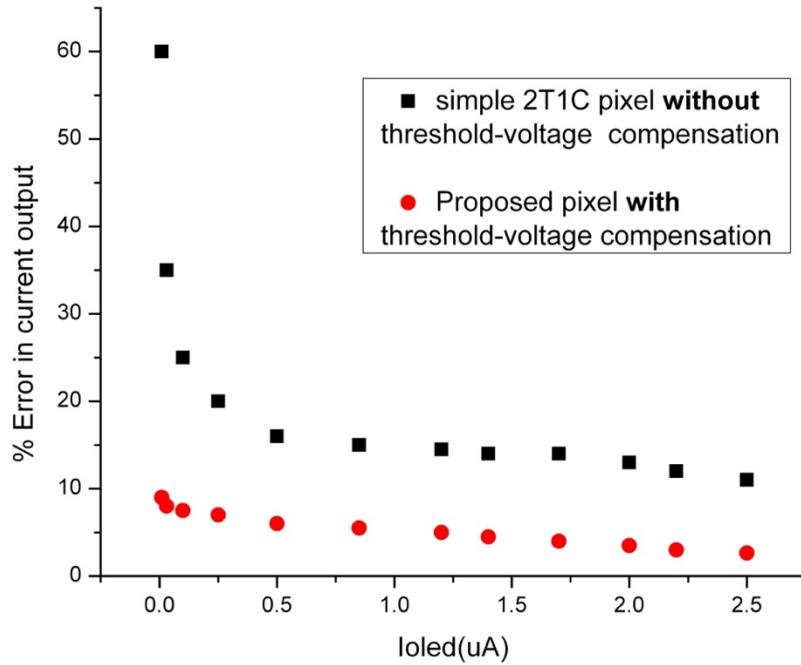

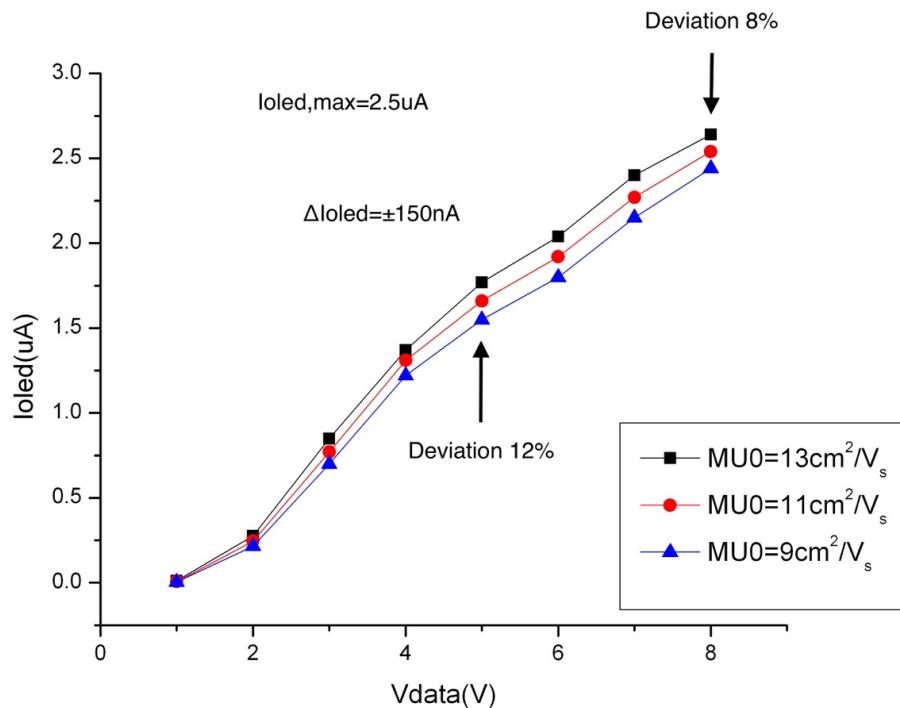

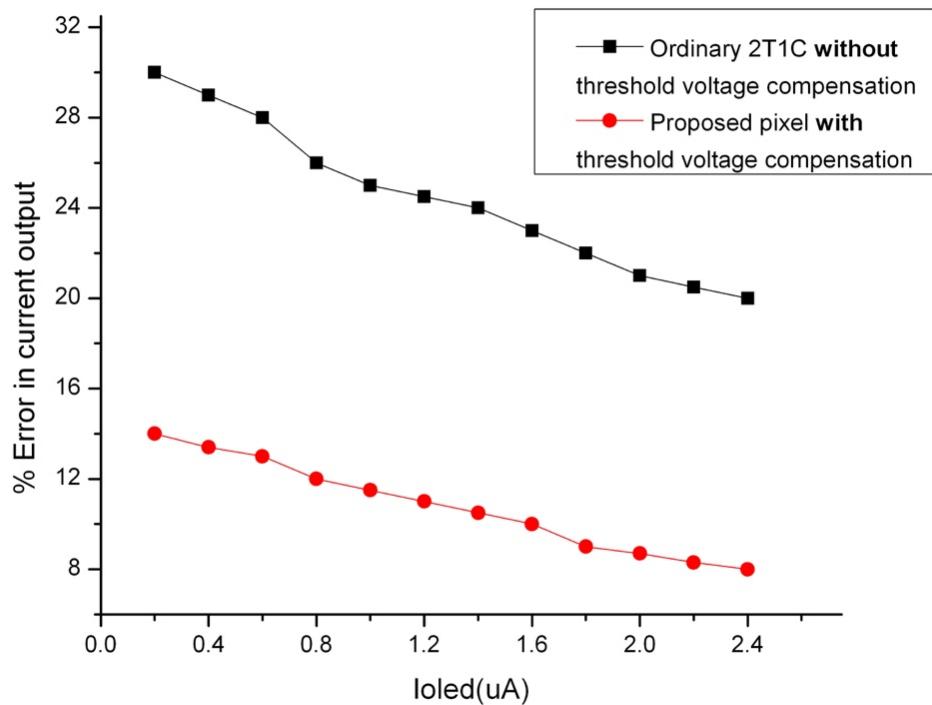

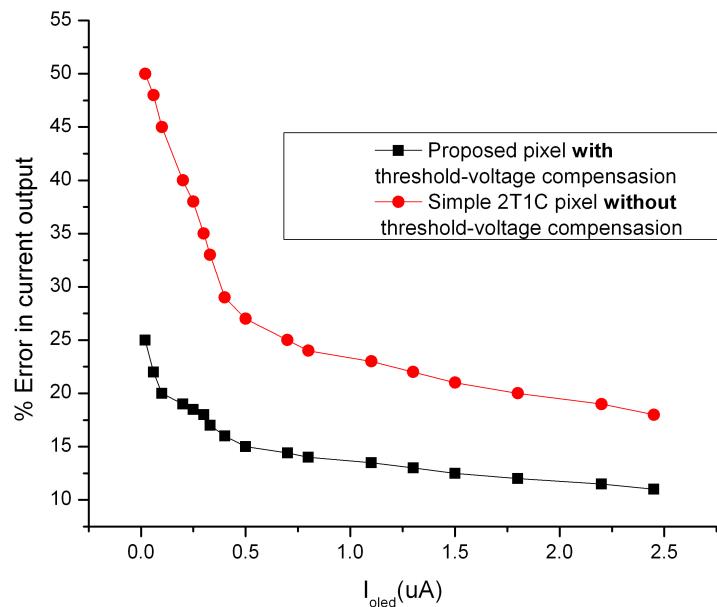

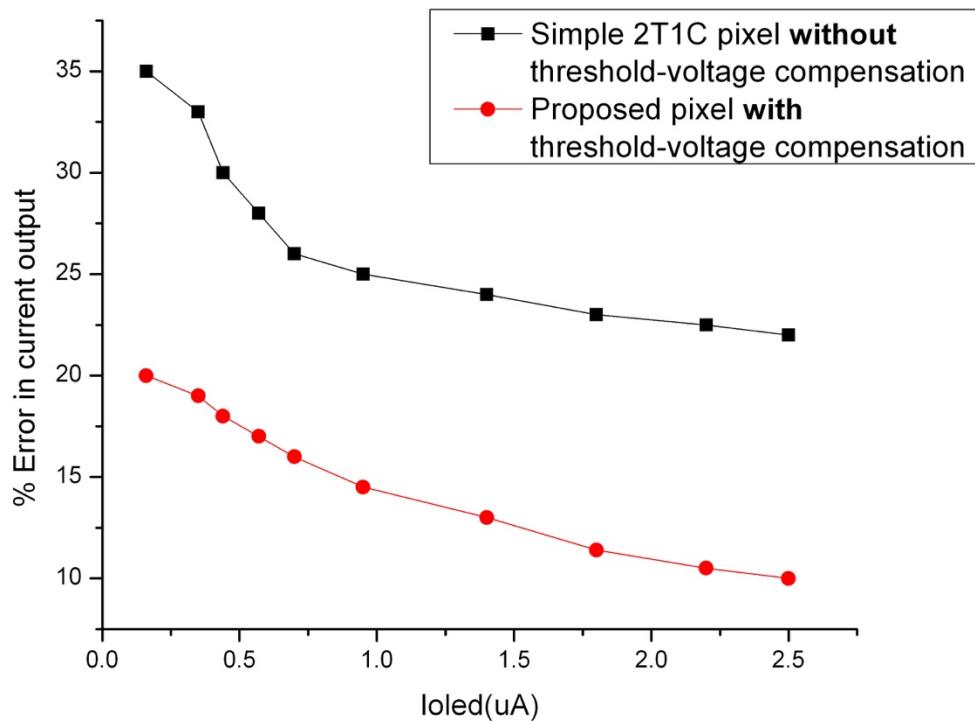

The fifth chapter is a presentation of the results of the simulations. First, the results are calculated for the variation of threshold-voltages, as well as the variation of carriers mobility to measure the final deviation of the current at the

driving TFT Ioled. These measurements are repeated for IGZO as well as the LTPS model, and subsequently differences between the models on the proposed pixel circuit are presented. Furthermore, a LAYOUT of the proposed pixel design is presented. Finally, there is a study on the power consumption for two cases: the full bright display and the half bright display.

In the sixth chapter, a comparison between our proposed pixel design and four other different circuits is presented, regarding the results of each of those circuits. Indications for further future projects are exposed based on our findings, mainly concerning VR displays. The final conclusions are presented in the end of this chapter.

## GREEK ABSTRACT

Το θέμα της παρούσας διπλωματικής εργασίας είναι η σχεδίαση ενός προγραμματιζόμενου κυκλώματος pixel με τάση για Active Matrix Organic Light Emitting Diode (AMOLED) οθόνη. Ειδικότερα, χρησιμοποιήθηκε μια νέα τεχνική σχεδίασης για την αναίρεση των επιδράσεων της μεταβολής της τάσης κατωφλίου. Το προτεινόμενο κύκλωμα είναι μια παραλλαγή του συμβατικού κυκλώματος 2T1C (2 τρανζίστορ – 1 πυκνωτής) και ένα βασικό του πλεονέκτημα είναι ότι αποτελείται από τέσσερα τρανζίστορ και έναν πυκνωτή, κάτι που το καθιστά ιδιαίτερα απλό στη σχεδίασή του.

Τα τελικά αποτελέσματα για τη μεταβολή της τάσης κατωφλίου επιβεβαιώθηκαν με προσομοιώσεις. Το κύριο πλεονέκτημα του προτεινόμενου σχεδιασμού pixel είναι ότι το ρεύμα του OLED είναι ανεξάρτητο από την τάση κατωφλίου του TFT και είναι καλά ελεγχόμενο. Επίσης, η τεχνική αναίρεσης της τάσης κατωφλίου εφαρμόζεται με ένα στατικό κύκλωμα, με αποτέλεσμα έναν ιδιαίτερα γρήγορο χρόνο απόκρισης, παρόμοιο με το χρόνο απόκρισης του συμβατικού pixel 2T1C που είναι το ταχύτερο κύκλωμα.

Στο πρώτο κεφάλαιο της εργασίας παρουσιάζεται η τεχνολογία των τρανζίστορ λεπτού υμενίου (Thin Films Transistors - TFTs) καθώς η τεχνολογία αυτή αποτελεί την κυρίαρχη τεχνολογία στον τομέα των οθονών. Αρχικά, γίνεται μια εισαγωγή στα TFT, με αναφορές στην σπουδαιότητα χρήσης τους σε οθόνες, τον τρόπο και τις περιοχές λειτουργίας τους, καθώς επίσης και στις διαφορές τους με τα Metal Oxide Semiconductor Field-effect Transistor (MOSFET). Αναφέρονται οι λόγοι για τους οποίους τα TFT είναι απαραίτητα στο σχεδιασμό οθονών, αναλύεται η δομή τους, ενώ περιγράφεται μέσω μιας σύντομης ιστορικής ανασκόπησης η εξέλιξή τους και αναπτύσσονται τα διαφορετικά είδη τεχνολογίας TFT. Συγκεκριμένα αναλύεται η βελτίωση των χαρακτηριστικών των TFT, καθώς και η διαδικασία κατασκευής που χρησιμοποιείται στη βιομηχανία επίπεδων οθονών. Τέλος, παρατίθενται μοντέλα πυριτίου, όπως το άμορφο πυρίτιο (a-Si), το πολυκρυσταλλικό πυρίτιο (poly-Si), το οξείδιο ψευδαργύρου ινδίου γαλλίου (indium gallium zinc oxide -IGZO) και συγκρίνονται τα πλεονεκτήματα και τα μειονεκτήματά τους.

Στο δεύτερο κεφάλαιο παρουσιάζονται διάφοροι τύποι οθονών όπως οι CRT (Cathode Ray Tube) – LCD (Liquid Crystal Display) - OLED (Organic Light Emitting Diode), με μια σύντομη ιστορική ανασκόπησή τους. Συγκεκριμένα, περιγράφονται τα βασικά χαρακτηριστικά προβολής κάθε οθόνης και συγκρίνονται μεταξύ τους. Ειδικότερα, παρουσιάζεται η λειτουργία του μοντέλου OLED που χρησιμοποιείται για τις προσομοιώσεις και αναπτύσσονται τα πλεονεκτήματα και τα μειονεκτήματα των οθονών LCD και OLED.

Επιπλέον, σε αυτό το κεφάλαιο παρουσιάζονται οι μέθοδοι διευθυνσιοδότησης για τις οθόνες. Οι μέθοδοι αυτές έχουν να κάνουν με τον τρόπο επικοινωνίας του pixel με τον επεξεργαστή και είναι: η απευθείας (Direct), η παθητική (Passive) και η ενεργή (Active) μέθοδος. Στη συνέχεια συγκρίνονται οι δύο βασικές μέθοδοι διευθυνσιοδότησης, η ενεργή και η παθητική. Καθώς η ενεργή μέθοδος διευθυνσιοδότησης εμφανίζει τα περισσότερα πλεονεκτήματα στις σύγχρονες οθόνες, περιγράφεται αναλυτικότερα η αρχιτεκτονική της.

Στο τρίτο κεφάλαιο αναλύεται η λειτουργία του OLED pixel το οποίο παρέχει μια καλύτερη λύση στο σχεδιασμό των εικονοστοιχείων για λεπτότερες οθόνες υψηλής απόδοσης και μικρότερης κατανάλωσης. Οι τελευταίας γενιάς οθόνες δημιουργούνται με εφαρμογή της ενεργής μεθόδου διευθυνσιοδότησης (AMOLED). Περιγράφονται και συγκρίνονται δύο διαφορετικοί τρόποι παραγωγής χρωμάτων σε OLED οθόνες, με έγχρωμα sub-pixel ή με λευκά sub-pixel και έγχρωμα φίλτρα τοποθετημένα στο επάνω μέρος τους. Επιπλέον, αναλύεται ο τρόπος προγραμματισμού των εικονοστοιχείων, με τάση ή με ρεύμα και συγκρίνονται οι δυο αυτοί τρόποι ώστε να διευκρινιστούν τα πλεονεκτήματα και τα μειονεκτήματά της κάθε σχεδίασης.

Στο τέλος του κεφαλαίου αυτού περιγράφεται η λειτουργία του συμβατικού και πιο απλού κυκλώματος 2T1C και η διαδικασία αναίρεσης της μεταβολής της τάσης κατωφλίου.

Στο τέταρτο κεφάλαιο περιγράφεται βήμα προς βήμα η σχεδίαση του προτεινόμενου κυκλώματος. Πρόκειται για ένα προγραμματιζόμενο κύκλωμα pixel με τάση για Voltage Programmed Pixel Circuit (VPPC) το οποίο έχει κάποιες τροποποιήσεις σε σχέση με το συμβατικό προγραμματιζόμενο με τάση κύκλωμα (2T1C -2 TFT και 1 Capacitor), όπως φαίνεται στο παρακάτω σχήμα.

Το pixel σχεδιάστηκε με τεχνολογία TFT για IGZO και LTPS μοντέλα. Το νέο κύκλωμα χρησιμοποιεί μια νέα τεχνική σχεδίασης για την αναίρεση των επιδράσεων της μεταβολής της τάσης κατωφλίου. Αναλύεται διεξοδικά η λειτουργία του κυκλώματος καθώς και οι προδιαγραφές σχεδίασής του. Λαμβάνοντας υπόψη ότι πρόκειται για μια μικρή οθόνη (5.2’’), το pixel θα πρέπει να σχεδιαστεί κάτω από μια αρκετά περιορισμένη περιοχή (pixel per inch- ppi) για Full HD οθόνη (1920x1080) και ο ρυθμός ανανέωσης Frame rate να είναι αρκετά υψηλός, δηλαδή 90Hz. Για το λόγο αυτό επιλέχθηκε το ελάχιστο πλάτος των TFT της προτεινόμενης τοπολογίας να είναι 2μm και το μήκος των τρανζίστορ να κυμαίνεται από 2 έως 10μm. Η τάση τροφοδοσίας του pixel για το IGZO μοντέλο είναι στα 10V, ενώ για το LTPS μοντέλο είναι στα 6V αντίστοιχα. Μετά από υπολογισμούς για την ελάχιστη επιτρεπτή χωρητικότητα του πυκνωτή αποθήκευσης  $C_s$ , ο πυκνωτής πρέπει να είναι 100fF. Η τάση  $Vctr$  επιλέχτηκε να είναι μια σταθερή τάση στα 3V ενώ ο παλμός  $V_{scan}$  είναι ρυθμισμένος στα  $V_{scan}=12V$ , ανεξάρτητα από το μοντέλο που γίνονται οι προσομοιώσεις. Η τιμή του  $Vdata$  στο IGZO μοντέλο έχει ένα εύρος τιμών από 1 έως 9V, ενώ για το LTPS μοντέλο από 2 έως 4V αντίστοιχα.

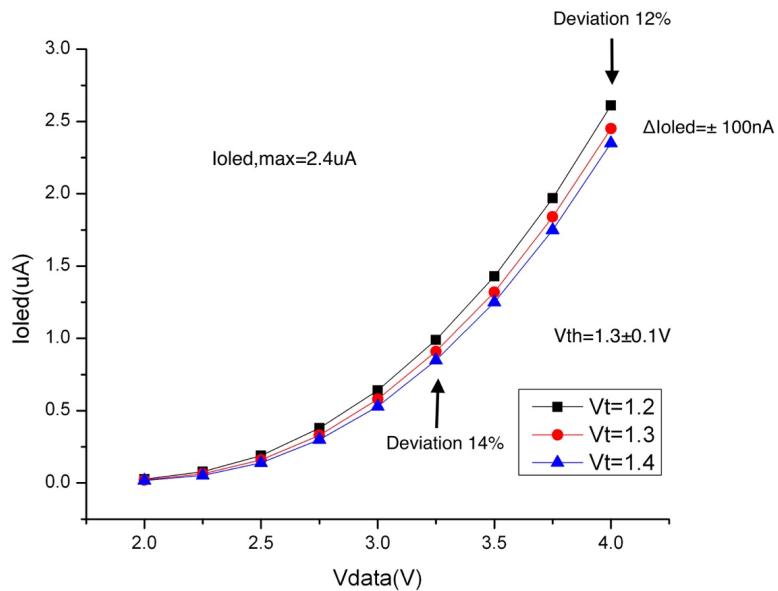

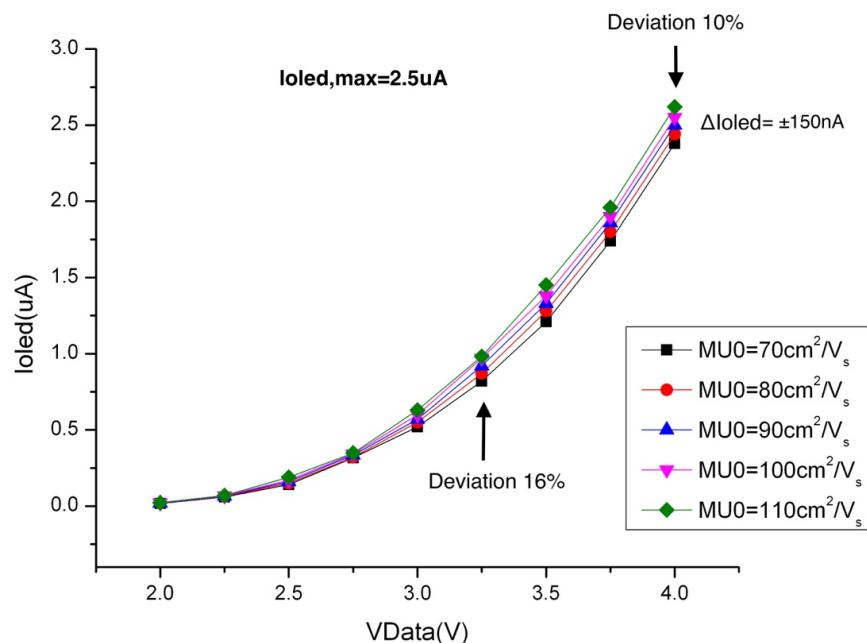

Η θεωρητική ανάλυση του προτεινόμενου pixel επιβεβαιώνεται στη συνέχεια με προσομοιώσεις, χρησιμοποιώντας τη σουίτα *virtuoso* της εταιρίας *cadence*. Οι αναλύσεις των προσομοιώσεων αφορούν τη μεταβολή της τάσης

κατωφλίου ( $V_t$ ) και τη μεταβολή της ευκινησίας φορέων ( $MU0$ ) για τη μέτρηση της τελικής απόκλισης του ρεύματος Ioled από το TFT οδήγησης. Οι μετρήσεις αυτές γίνονται αρχικά για το IGZO μοντέλο και στη συνέχεια για το LTPS μοντέλο. Στη συνέχεια, στο προτεινόμενο κύκλωμα pixel και για ακριβώς τις ίδιες διαστάσεις των TFT, παρουσιάζονται οι διαφορές ανάμεσα στα δύο αυτά μοντέλα.

Οι αναλύσεις των προσομοιώσεων έδειξαν εντυπωσιακή μείωση του σφάλματος στο ρεύμα εξόδου ( $I_{OLED}$ ) στην περίπτωση του IGZO μοντέλου, καθώς επίσης και ότι το ρεύμα εξόδου, για διαφορετικές τάσεις κατωφλίου, είναι ανεξάρτητο από την τάση κατωφλίου ( $V_t$ ), όπως προκύπτει από τον τύπο στον οποίο καταλήξαμε:  $I_{OLED} = \frac{W}{2L} \mu C_{ox} (V_{DATA} - V_{CTR})^2$ . Η μέγιστη τιμή του Ioled ρεύματος επιλέξαμε να είναι  $2.4 \mu A$  και στα δύο μοντέλα IGZO και LTPS, σε όλες τις προσομοιώσεις.

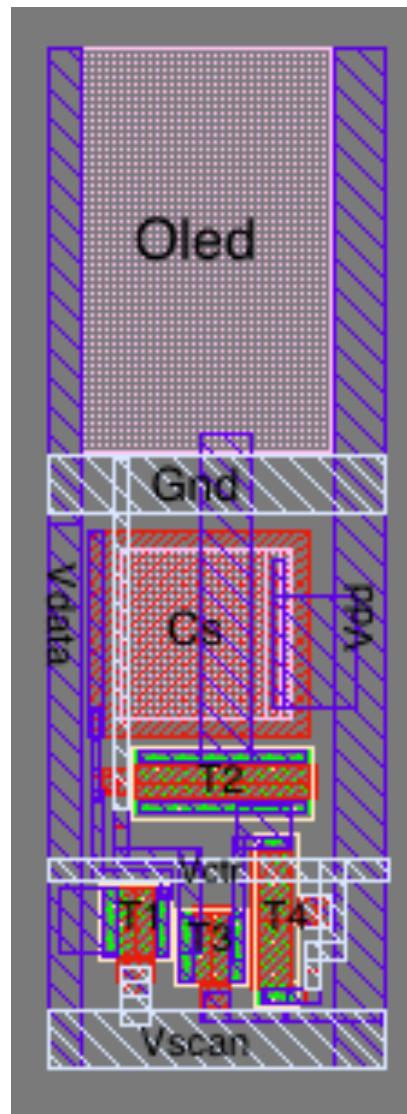

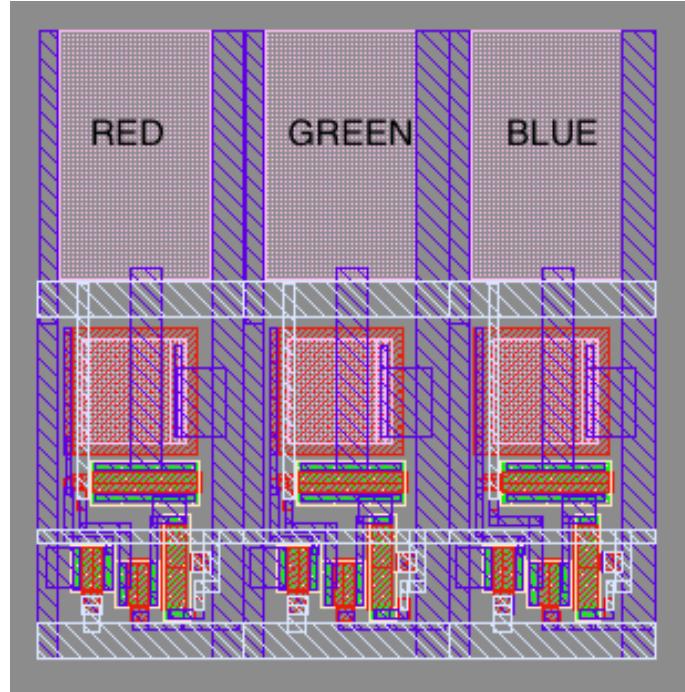

Στην συνέχεια περιγράφεται το layout του προτεινόμενου pixel για το οποίο χρησιμοποιήθηκε το περιβάλλον layout XL από τη συνίτια του virtuoso cadence. Δυσκολότερο μέρος του σχεδιασμού αποτελούσε η εξαιρετικά μικρή περιοχή του pixel, λόγω των προδιαγραφών της οθόνης Full HD. Έτσι, η περιοχή του κάθε sub-pixel όφειλε να είναι  $60 \times 20 \text{ } \mu\text{m}^2$  και το Aperture ratio ήταν 40%. Αυτό συνεπώς σήμαινε ότι η διαθέσιμη περιοχή για το κύκλωμα ήταν μόνο  $36 \times 20 \text{ } \mu\text{m}^2$ .

Τα υλικά που χρησιμοποιήθηκαν για τη διάταξη των εικονοστοιχείων ήταν δύο είδη μετάλλου (MET1 & MET2) και ένα πολυ-πυριτίου (POLY1). Επιπλέον, κάτι στο οποίο έπρεπε να δοθεί ιδιαίτερη έμφαση, κατά τη σχεδίαση του layout, ήταν τα τρανζίστορ T2 και T4 να είναι το δυνατότερο πιο κοντά το ένα στο άλλο, ώστε να έχουν ακριβώς την ίδια τάση κατωφλίου. Με τον τρόπο αυτό, γίνεται σωστά η αναίρεση των μεταβολών της τάσης κατωφλίου ( $V_t$ ).

Στη συνέχεια, υπολογίστηκε η κατανάλωση για τις εξής δύο περιπτώσεις: την πλήρη φωτεινότητα και τη μισή φωτεινότητα στην οθόνη. Στην περίπτωση της πλήρους φωτεινότητας, η κατανάλωση στο μοντέλο IGZO είναι  $72 \text{ } \mu\text{W}$  ενώ για το μοντέλο LTPS είναι  $43,2 \text{ } \mu\text{W}$ . Αυτό σημαίνει ότι υπάρχει εξοικονόμηση ενέργειας της τάξης του 66%. Στη δεύτερη περίπτωση, της μισής φωτεινότητας, η συνολική κατανάλωση παραμένει μικρότερη στο μοντέλο LTPS. Για την ακρίβεια, είναι  $38 \text{ } \mu\text{W}$  για το μοντέλο IGZO και  $22 \text{ } \mu\text{W}$  για το μοντέλο LTPS.

Συνεπώς, υπάρχει εξοικονόμηση ενέργειας ύψους 75%. Αυτό οφείλεται στο γεγονός ότι με το μοντέλο LTPS η τάση τροφοδοσίας είναι αρκετά μικρότερη και επίσης το εύρος των τιμών της τάσης δεδομένων (Vdata) είναι αρκετά μικρότερο από το μοντέλο IGZO.

Η εργασία ολοκληρώνεται επισημαίνοντας κάποιες διαφοροποιήσεις ώστε να γίνει εφικτή η χρήση του pixel σε virtual reality (VR) οθόνες, που θεωρούνται οι πλέον υψηλής τεχνολογίας συσκευές.

# Table of Contents

|                                                                                                         |           |

|---------------------------------------------------------------------------------------------------------|-----------|

| <b>CHAPTER ONE Thin-Film Transistors (TFT).....</b>                                                     | <b>15</b> |

| 1.1 Introduction.....                                                                                   | 16        |

| 1.2 Structure of TFTs.....                                                                              | 16        |

| 1.3 Operation of TFTs .....                                                                             | 18        |

| 1.4 Historical Overview .....                                                                           | 20        |

| 1.5 Models of Si.....                                                                                   | 21        |

| 1.5.1 <i>Amorphous silicon – a-Si.....</i>                                                              | 22        |

| 1.5.2 <i>Low-temperature polycrystalline silicon - LTPS.....</i>                                        | 22        |

| 1.5.3 <i>Indium gallium zinc oxide – IGZO.....</i>                                                      | 23        |

| <b>CHAPTER TWO: DISPLAYS .....</b>                                                                      | <b>27</b> |

| 2.1 Introduction.....                                                                                   | 28        |

| 2.2 Historical Overview .....                                                                           | 29        |

| 2.3 Types of flat displays.....                                                                         | 30        |

| 2.3.1 <i>Liquid Crystal Displays – LCD.....</i>                                                         | 30        |

| 2.3.2 <i>Organic Light-Emitting Display – OLED.....</i>                                                 | 33        |

| 2.3.3 <i>Comparison of the displays features.....</i>                                                   | 36        |

| 2.4 Addressing Methods of Flat Display .....                                                            | 37        |

| 2.4.1 <i>Direct addressing method .....</i>                                                             | 37        |

| 2.4.2 <i>Passive matrix addressing method .....</i>                                                     | 38        |

| 2.4.3 <i>Active Matrix addressing method .....</i>                                                      | 39        |

| 2.5 The Peripheral Circuit Driving Architecture of Active Matrix Display .....                          | 40        |

| 2.5.1 <i>Architecture of Active Matrix Display .....</i>                                                | 41        |

| 2.5.2 <i>Gate / Row Driver Circuits.....</i>                                                            | 42        |

| 2.5.3 <i>Data/Column Driver Circuits .....</i>                                                          | 43        |

| <b>CHAPTER THREE: Organic Light Emitting Diode .....</b>                                                | <b>46</b> |

| 3.1 Introduction.....                                                                                   | 47        |

| 3.2 Programming methods.....                                                                            | 51        |

| 3.2.1 <i>Current Programming Method.....</i>                                                            | 51        |

| 3.2.2 <i>Voltage Programming Method .....</i>                                                           | 53        |

| 3.3 Design Techniques AMOLED Pixel for Cancelling the Effect of the Variation of Threshold Voltage..... | 55        |

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>CHAPTER FOUR: Pixel Design .....</b>                        | <b>57</b> |

| 4.1 Introduction.....                                          | 58        |

| 4.2 Circuit operation .....                                    | 60        |

| 4.3 Design specifications .....                                | 62        |

| 4.4 Pixel Response Time Analysis .....                         | 63        |

| <b>CHAPTER FIVE SIMULATION RESULTS.....</b>                    | <b>69</b> |

| 5.1 Introduction.....                                          | 70        |

| 5.2 Indium Gallium Zinc Oxide (IGZO) model .....               | 70        |

| 5.2.1 <i>Threshold Voltage variations for IGZO model</i> ..... | 71        |

| 5.2.2 <i>Carriers mobility variations for IGZO model</i> ..... | 73        |

| 5.3 Low-Temperature Polycrystalline Silicon (LTPS) model ..... | 77        |

| 5.3.1 <i>Threshold Voltage variations for LTPS model</i> ..... | 78        |

| 5.3.2 <i>Carriers mobility variations for LTPS model</i> ..... | 79        |

| 5.4 LAYOUT .....                                               | 81        |

| 5.5 Power Consumption.....                                     | 83        |

| 5.5.1 <i>Full brightness</i> .....                             | 84        |

| 5.5.2 <i>Half brightness</i> .....                             | 84        |

| 5.5.3 <i>Conclusions</i> .....                                 | 85        |

| <b>CHAPTER SIX CONCLUSIONS AND DISCUSSION.....</b>             | <b>86</b> |

| 6.1 Comparison with other circuits.....                        | 87        |

| 6.2 Suggested future project .....                             | 97        |

| 6.3 CONCLUSIONS .....                                          | 98        |

| References .....                                               | 100       |

# **CHAPTER ONE:**

## **Thin-Film Transistors (TFT)**

## 1.1 Introduction

Nowadays, Thin-Film Transistor (TFTs) technology is dominant in the area of displays. It is used to fabricate small watch screens under 1 inch to computer monitors and television screens for several inches. The displays that use TFTs, replaced the Cathode Ray Tube screens (CRTs) both because of the large volume of the last ones (need a cannon for emitting electrons) and secondly because TFTs displays possess superior features, such as sharpness, resolution, frame rate, response time, contrast ratio, viewing angle [1].

A display screen made with Thin-Film Transistor (TFT) technology, having a transistor at each pixel, means that the current, which triggers pixel illumination, can be smaller and therefore can be switched on and off more quickly.

The development of TFTs made possible the creation both of flexible screens and transparent screens. In these two areas is focused the most recent research. Furthermore, semiconductor materials enabling faster TFTs, such as low- temperature polycrystalline silicon (LTPS) or transparent semiconducting oxides (TSOs), hold the promise of expanding TFT application to gate and data drivers or even full systems-on-panel, for increased reliability and lower production costs.

## 1.2 Structure of TFTs

A TFT is a field-effect transistor (FET) contains three terminals (gate, source, and drain) and it includes semiconductive, dielectric, and conductive layers. The semiconductor is located between source and the drain electrodes and the dielectric is placed between the gate electrode and the semiconductor. This device can control the current between drain and source ( $I_{DS}$ ) by varying the potential between gate and source ( $V_{GS}$ ). It also produces free charge accumulation at the dielectric and semiconductor interface [2].

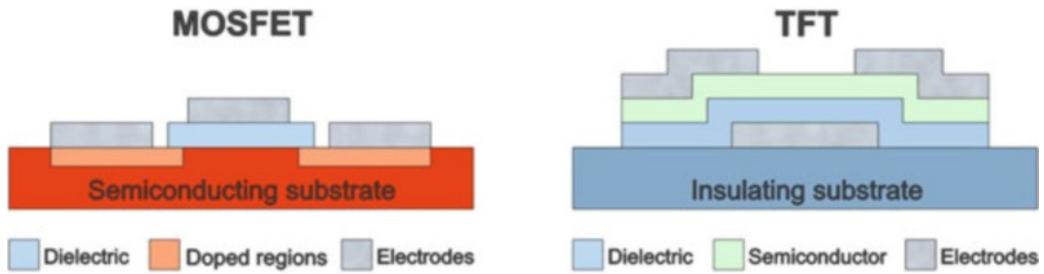

In TFTs the main emphasis is on large area and low temperature processing, while metal oxide semiconductor field-effect transistors (MOSFETs) are basically concentrated in high performance, with considerably larger processing temperature.

As it is shown in fig. 1.1, MOSFETs use a silicon wafer, acting as substrate and semiconductor, while, TFTs use an insulator substrate, such as glass, that is not an active element for device operation. Furthermore, MOSFETs and TFTs have different operation mode.

Fig. 1.1: Comparison of typical structures of MOSFETs and TFTs

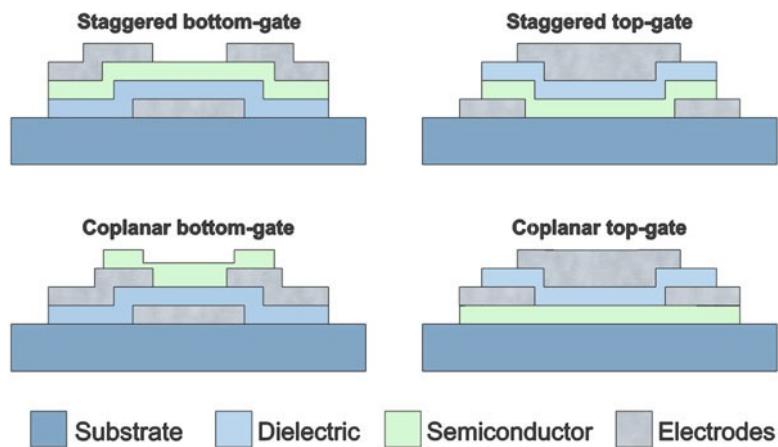

The former is based on inversion, while the latter relies on accumulation. In fig. 1.2 is shown the four TFT structures according on the position of the layers. They can either be staggered or coplanar (whether drain/source and gate are on opposite or on the same side regarding the semiconductor) and, inside them, top or bottom gate (according to the location of gate) [3].

Fig. 1.2: The most typical TFT structures depending on the positioning of layers

Each of these four structures has advantages and negatives and in terms of fabrication the choice for one of these structures depends on the deposition processes and/or post-processing temperatures or number of lithographic masks

involved. For example, staggered bottom-gate structures are typically used when the dielectric layer requires high temperature, while coplanar top-gate ones are common for high temperature semiconductors, such as poly-Si [4].

Regarding operation and considering n-type TFTs, these can be designated by enhancement or depletion mode depending if threshold voltage ( $V_T$ ) is positive or negative. An increase in quality mode is typically preferable because a gate voltage is not necessary to turn off the device (to achieve its Off-state) [5].

### 1.3 Operation of TFTs

Below will be describe the operation of TFTs, which is similar to that of the MOSFETs. Specifically, it will be examined the different cases of TFTs operation depending on the voltage existing at the gate-source  $V_{GS}$ .

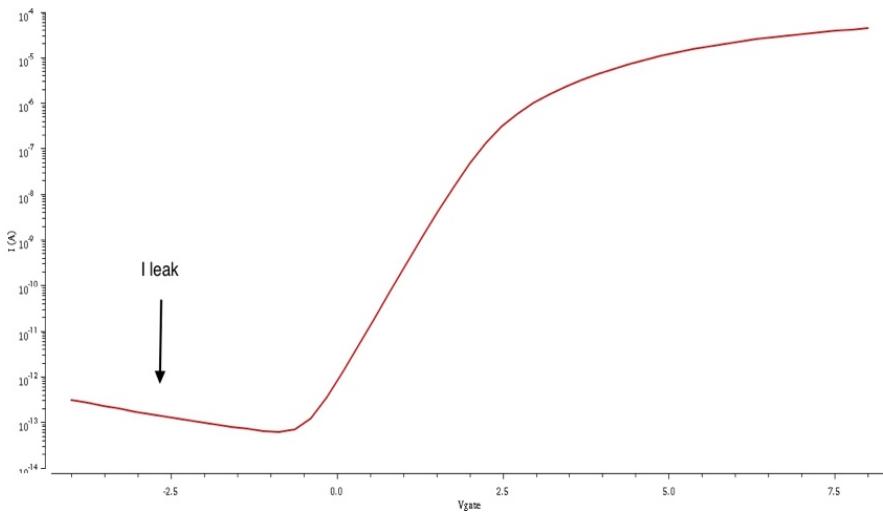

As it is shown in fig 1.3, the transistor's *Cut-Off Region* specified on gate voltage, much lower than the threshold voltage of the transistor. Therefore, the condition to operate an n-type transistor in the *Cut-Off* is:  $V_{GS} \ll V_T$ , where  $V_{GS}$  is the voltage between the gate potential and the corresponding source and  $V_{TH}$  is the threshold voltage of the transistor. In this region, the drain currents derived from leakage currents mechanisms.

$$I_{leak} = I_o \cdot W \cdot \left[ \exp\left(\frac{q \cdot BLK \cdot V_{DS}}{k \cdot T}\right) - 1 \right] \cdot (X_{TFE} + X_{TE}) + I_{diode} \quad (1.1)$$

where  $W$ , the channel length,  $I_o$  and  $BLK$  constants, the product  $kT / q$  is the thermal energy of the actors and  $V_{DS}$ , the drain-source voltage. Also,  $X_{TFE}$ , is the effect of thermionic field emission of carriers through the grain boundary trap states and  $X_{TE}$ , the effect of thermal field emission of carriers through the grain boundary trap states.

In the first bracket the reduction of the potential barrier due to the influence of  $V_{DS}$  is calculated. This effect is described by the constant  $BLK$ .

Finally, the reverse biased diode current of the drain contact,  $I_{diode}$ , is given by:

$$I_{diode} = I_{oo} \cdot W \cdot \exp\left(\frac{-E_B}{kT}\right) \left[ 1 - \exp\left(\frac{-qV_{DS}}{kT}\right) \right] \quad (1.2)$$

where  $I_{oo}$  is a proportionality constant and  $E_B$  is the potential barrier of the p-n contact.

When  $V_{GS} > V_T$ , a significant density of electrons is accumulated in

dielectric/semiconductor interface and a large  $I_{DS}$  starts flowing, depending on the drain-to-source potential ( $V_{DS}$ ). This state is designated by On-state and involves two main regions depending on the  $V_{DS}$  value:

- If  $V_{DS} < V_{GS} - V_T$ , the TFT is in linear/triode mode and  $I_{DS}$  is described by:

$$I_{DS} = C_i \mu_{FE} \frac{W}{L} [(V_{GS} - V_T)V_{DS} - \frac{1}{2}V_{DS}^2] \quad (1.3)$$

where  $C_i$  is the gate capacitance per unit area,  $\mu_{FE}$  the field-effect mobility,  $W$  the channel width, and  $L$  the channel length of the device. For  $V_{DS} \ll V_{GS} - V_T$  the quadratic term is typically neglected.

- if  $V_{DS} > V_{GS} - V_T$ , the device is in saturation mode.  $I_{DS}$  is independent of  $V_{DS}$  and is described by:

$$I_{DS} = \frac{1}{2} C_i \mu_{sat} \frac{W}{L} (V_{GS} - V_T)^2, \quad (1.4)$$

where  $\mu_{sat}$  is the saturation mobility.

Fig. 1.3.  $I_{DS}$  as a function of  $V_{GS}$  for different values of the drain-source voltage  $V_{DS} = 5, 10$  and  $20$  V showing the different regions of operations

A typical characterization of TFTs involves static-current voltage measurements where output and transfer curves are obtained, as shown in fig. 1.3. While the output curve provides mostly a qualitative information regarding the effectiveness of channel pinch-off (hence saturation) and contact resistance, the transfer curve offers a more quantitative analysis.

## 1.4 Historical Overview

The twentieth century is characterized by the birth of electronic technology. One of the main achievement is the development of Thin-Film Transistors (TFTs), which are the main elements of the electronic flat panel displays industry. Starting with Lilienfeld in early forties, the first TFTs, as metal semiconductor field-effect transistor (MESFET) and some years later, as metal insulator semiconductor field-effect transistor (MISFET), in the coming decades have taken place very important strides in their development [6].

A main discovery for the modern electronics world was the first attempt for implementing a TFT device in 1947 by Bardeen and Brattain. It was a thin-film field effect device used a germanium film. A second main discovery, the junction field-effect transistor (JFET) was realized by Borkan and Weimer (1963) and it was based on Shockley's JFET analysis in 1952. Polycrystalline cadmium sulphide (CdS) was the material that used for the thin-film and silicon monoxide was the insulator. Source and drain contacts were placed on the opposite side of the gate. These were the first transistors that were actually fabricated, showing the switching capability of such devices and how they could be advantageous over the conventional tubes [7].

In the seventies, first, the implementation of a thin-film semiconductor instead of crystalline bulk silicon material, like Cadmium Selenide (CdSe), and second, the Active Matrix addressing method proposed by Lechner (1971) and the fact that the switch device needed in each pixel of the matrix can be materialized with the use of a TFT device, were the two very important events that changed the perspectives for TFTs. The result of the last implementation was the reduction of the fabrication cost and the decrease of the transistor size. Thin-film, formed with a-Si:H, have no grain boundaries and it was the most cost-effective technology. However, the main disadvantage of this technology was the low mobility of the carriers and the instability of the device electrical characteristics.

In the next decade the TFT technology developed rapidly. Amorphous hydrogenated silicon (a-Si:H) was introduced as a semiconductor on TFTs. Despite its low mobility when compared with the (poly) crystalline materials being studied in that period, the amorphous structure allowed for large area

fabrication, which together with the good switching capability of this technology was of great importance in defining a-Si:H TFTs as the main choice for the fabrication of active matrix liquid crystal displays (AMLCDs).

In early eighties, Lueder (1980) introduced a new approach in the TFT fabrication process. Photolithography was used instead of shadow masks that were being used since then. Their devices were optimized for liquid crystal displays applications, since the photolithography process made source-drain contacts that were self-aligned to the gate, causing the gate-source parasitic capacitance to be reduced. The compensation of the parasitic effects has improved the performance of the TFT-LCDs in the terms of the response time and the image quality. Furthermore, Depp (1981) from IBM proposed a polycrystalline silicon active layer. Pursuing greater mobility devices, TFTs based on poly-Si were introduced, allowing for high performance circuit fabrication. However, poly-Si TFTs required high temperature processes and had high fabrication cost [7].

Therefore, in the nineties, organic TFTs also appeared with a great advantage, low processing temperature, although their lack of stability and performance still remains an issue these days. Hence, for the next decades, there was still area for a new technology, combining large area uniformity, low processing temperatures, and good electrical performance.

Subsequently, the research of the TFT technology was concentrated on the improvement of the TFT devices characteristics and their fabrication process. Amorphous and polycrystalline silicon TFTs were the two main technologies that were used in the flat panel display industry. In the last decade, new TFTs technologies have been announced, like Indium gallium zinc oxide – IGZO, metamorphous silicon and organic TFTs.

## 1.5 Models of Si

Backplane technology describes the materials and assembly designs used for the thin film transistors which drive the main display. In other words, it is the backplane that contains an array of transistors which are responsible for turning

the individual pixels on and off, acting therefore as a determining factor when it comes to display resolution, refresh rate, and power consumption.

Examples of backplane technology include amorphous silicon (aSi), low-temperature polycrystalline silicon (LTPS) and indium gallium zinc oxide (IGZO), whilst LCD and OLED are examples of light emitting material types. Some of the different backplane technologies can be used with different display types, so IGZO can be used with either LCD or OLED displays, albeit that some backplanes are more suitable than others.

### ***1.5.1 Amorphous silicon – a-Si***

Amorphous silicon has been the go-to material for backplane technology for many years, and comes in a variety of different manufacturing methods, to improve its energy efficiency, refresh speeds, and the display's viewing angle. Today, a-Si displays is only a small percentage of the smartphone display market.

For mobile phone displays with a pixel density lower than 300 pixels per inch (PPI), this technology remains the preferable backplane of choice, mainly due to its low costs and relatively simple manufacturing process. However, when it comes to higher resolution displays and new technologies such as AMOLED, a-Si is beginning to struggle.

AMOLED puts more electrical stress on the transistors compared with LCD, and therefore favors technologies that can offer more current to each pixel. Also, AMOLED pixel transistors take up more space compared with LCDs, blocking more light emissions for AMOLED displays, making a-Si rather unsuitable. As a result, new technologies and manufacturing processes have been developed to meet the increasing demands made of display panels over recent years.

### ***1.5.2 Low-temperature polycrystalline silicon - LTPS***

Recently LTPS sits as the high-bar of backplane manufacturing, and can be spotted behind most of the high end LCD and AMOLED displays found in today's smartphones. It is based on a similar technology to a-Si, but a higher process temperature is used to manufacture LTPS, resulting in a material with improved electrical properties.

LTPS is in fact the only technology that really works for AMOLED right now, due to the higher amount of current required by this type of display technology. LTPS also has higher electron mobility, which, as the name suggests, is an indication of how quickly/easily an electron can move through the transistor, with up to 100 times greater mobility than a-Si.

For starters, this allows for much faster switching display panels. The other big benefit of this high mobility is that the transistor size can be shrunk down, while still providing the necessary power for most displays. This reduced size can either be put towards energy efficiencies and reduced power consumption, or can be used to squeeze more transistors in side by side, allow for much greater resolution displays. Both of these aspects are becoming increasingly important as smartphones begin to move beyond 1080p, meaning that LTPS is likely to remain a key technology for the foreseeable future.

The drawback of LTPS TFT comes from its increasingly complicated manufacturing process and material costs, which makes the technology more expensive to produce, especially as resolutions continue to increase. As an example, a 1080p LCD based on this technology panel costs roughly 14 percent more than a-Si TFT LCD. However, LTPS's enhanced qualities still mean that it remains the preferred technology for higher resolution displays.

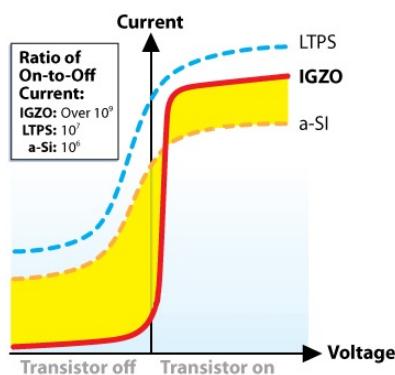

### ***1.5.3 Indium gallium zinc oxide – IGZO***

Currently, a-Si and LTPS LCD displays make up the largest combined percentage of the smartphone display market. However, IGZO is anticipated as the next technology of choice for mobile displays. Sharp originally began production of its IGZO-TFT LCD panels back in 2012, and has been employing its design in smartphones, tablets and TVs since then. The company has also recent shown off examples of non-rectangular shaped displays based on IGZO. Sharp isn't the only player in this field — LG and Samsung are both interested in the technology as well.

The area where IGZO, and other technologies, have often struggled is when it comes to implementations with OLED. a-Si has proven rather unsuitable to drive OLED displays, with LTPS providing good performance, but at increasing

expense as display size and pixel densities increase. The OLED industry is on the hunt for a technology which combines the low cost and scalability of a-Si with the high performance and stability of LTPS, which is where IGZO comes in.

This technology has quite a lot of potential, especially for mobile devices. IGZO's build materials allow for a decent level of electron mobility, offering 20 to 50 times the electron mobility of amorphous silicon (a-Si), although this isn't quite as high as LTPS, which leaves you with quite a few design possibilities. IGZO displays can therefore be shrunk down to smaller transistor sizes, resulting in lower power consumption, which provides the added benefit of making the IGZO layer less visible than other types. That means you can run the display at a lower brightness to achieve the same output, reducing power consumption in the process.

One of IGZO's other benefits is that it is highly scalable, allowing for much higher resolution displays with greatly increased pixel densities. Sharp has already announced plans for panels with 600 pixels per inch. This can be accomplished more easily than with a-Si TFT types due to the smaller transistor size.

Higher electron mobility also lends itself to improved performance when it comes to refresh rate and switching pixels on and off. Sharp has developed a method of pausing pixels, allowing them to maintain their charge for longer periods of time, which again will improve battery life, as well as help create a constantly high quality image.

Fig. 1.4. Note the transistors at the top of each colored pixel

Smaller IGZO transistors are also touting superior noise isolation compared

to a-Si, which should result in a smoother and more sensitive user experience when used with touchscreens.

The Table 1.1, below, lists the attributes of different fabrication technologies of the pixel circuits [8].

Table 1

Comparison of TFT backplane technologies for large-area electronics

| Attribute                           | a-Si:H | Oxide                   | Poly-Si                 | mc/nc-Si:H              | Organic     | IGZO            |

|-------------------------------------|--------|-------------------------|-------------------------|-------------------------|-------------|-----------------|

| Circuit type                        | n-type | n-type                  | n-type/p-type           | n-type/p-type           | p-type      | n-type          |

| Mobility (cm <sup>2</sup> /Vs)      | < 1    | ~10                     | 10~100                  | ~1-10                   | << 1        | ~10-20          |

| Temporal stability ( $\Delta V_T$ ) | issue  | more stable than a-Si:H | more stable than a-Si:H | more stable than a-Si:H | improving   | improving       |

| Initial uniformity                  | high   | higher than poly-Si     | low                     | potentially high        | low         | low             |

| Manufacturability                   | mature | developing              | developing              | research                | research    | Research        |

| Cost                                | low    | low                     | high                    | low                     | potentially | similar to a-Si |

The pixel circuits discussed above can be fabricated using different technologies, notably, poly silicon (poly-Si) and hydrogenated amorphous silicon (a-Si:H). Poly-Si technology offers high-mobility and complementary (n-type and p-type) TFTs, but has an undesirable large range of mismatched parameters over an array. This is due to the random distribution of the grain boundary in the material [9].

On the contrary, a-Si:H provides low mobility TFTs but does not provide p-type devices. Also, the threshold voltage of TFTs increases ( $V_T$ -shift) under prolonged bias stress due to the inherent instability of a-Si:H material. Besides, the technology provides good uniformity over a large area. Moreover, a-Si:H technology's industrial accessibility, by virtue of its usage in the AMLCD, provides for low-cost large-area electronics. In particular, an a-Si:H TFT backplane has the benefit of all the desirable attributes of the well-established a-Si:H technology, including low-temperature fabrication on plastic for eventual flexible electronics [10].

In addition, research is being carried out on new materials such as hydrogenated nano/micro crystalline (nc/mc) silicon, organic semiconductors and more recently, the highly promising amorphous oxide semiconductors. The nc/mc-Si:H and oxide semiconductor (e.g. indium gallium zinc oxide - IGZO) technologies provide higher temporal stability and mobility compared to the

ubiquitous a-Si:H technology [11]. However, light-induced instability can be an issue requiring special driving techniques for threshold-voltage recovery. Despite this a variety of analog and digital circuits have been demonstrated, including active matrix organic displays and imaging arrays [12].

On the other hand, an organic semiconductor has the potential for extremely low cost fabrication, including inkjet printing. However, this technology suffers from bias-induced and environment-induced instabilities and poor uniformity [13].

# **CHAPTER TWO:**

## **DISPLAYS**

## 2.1 Introduction

In the display technology, the information transmission plays the major role. In the monitor industry, the Cathode Ray Tube (CRT) has been the dominant display technology until the end of the last century. The CRT is a vacuum tube that contains one electron gun and a phosphorescent screen, and is used to display images. and it modulates, accelerates, and deflects electron beams onto the screen to create the images. The images may represent electrical waveforms (oscilloscope), pictures (television, computer monitor), or others.

One of the display technologies that deservedly replaced CRTs is the Liquid-Crystal Displays (LCDs). LCD is a flat-panel display or other electronic visual display that uses the light-modulating properties of liquid crystals. Liquid crystals do not emit light directly. The LCD monitors are eterofotous, which means that it is necessary to have a light source to the back of the screen and substantially the pixels of the liquid crystal are playing the role of switches which sometimes allow the light to pass while other times cut it. LCDs are available to display arbitrary images (as in a general-purpose computer display) or fixed images with low information content, which can be displayed or hidden. They use the same basic technology, except that arbitrary images are made up of a large number of small pixels, while other displays have larger elements. LCDs are used in a wide range of applications including computer monitors, television, phone screens and many other [14].

Another technology that dominates the display technology is the Organic Light-emitting diode (OLED). The OLED technology is used to create digital displays in devices such as televisions, computer monitors, portable systems such as mobile phones, tablets, smart watches. An OLED is a light-emitting diode (LED) in which the emissive electroluminescent layer is a film of organic compound that emits light in response to an electric current. This layer of organic semiconductor is situated between two electrodes; typically, at least one of these electrodes is transparent. A major area of research is the development of white OLED devices for use in solid-state lighting applications.

## 2.2 Historical Overview

In the end of the twentieth century, there was an enormous growth in small portable applications, such as mobile phones, portable computers (laptops), tablets and smart watches. All these applications required the necessary adjustment of the display technology to them, but the large volume of the CRTs was their main disadvantage and has limited their use in these kinds of devices. Thus, a new type of monitors should be found to replace the CRT.

The most satisfactory solution there were flat screens to minimize the volume occupied by the displays in the systems. It took several years of work by engineers trying to find the most appropriate type of flat screen that could replace CRT displays. In the nineties, this problem has been solved with the introduction of liquid crystal displays (Liquid Crystal Displays - LCDs) materialized with thin film silicon transistor (Thin-Film Transistors - TFTs), which was a milestone in technology semiconductor and the display industry in general. The successful development of TFT-LCD screens was not accidental. Although both liquid crystal technology (LCs), and semiconductor technologies implemented on glass substrates for Large Area Electronics (TFTs) - such as silicon thin film transistor- were well known long before the 90's, it had to be done an extended research that has led to the definition of materials and manufacturing process that could combine the two technologies and result in the completion of a TFT-LCDs screen.

The TFT-LCDs were rapidly grown and dominated the displays industry until today. They can be used in an extremely wide range of our everyday life products, like mobile phone applications, navigation systems, notebook PCs, tablets and wide screen TVs. The integration of the TFT-LCD panel peripheral driving components with low-power CMOS blocks and, therefore, the compatibility with battery operation was the main reason for the ascendance of the TFT-LCD technology in small portable applications.

The TFT-LCD monitors are eterofotous, which means that it is necessary to have a light source to the back of the screen and substantially the pixels of the liquid

crystal are playing the role of switches which sometimes allow the passage of light and other times don't. The mandatory presence of the light source resulted in the increase of power consumption and the volume of the screen. This feature limits the technical characteristics of the screen. This was the reason that there have been made attempts to find a new type of screen which would be self-luminous. In 1987, the Tank and Van Slyke, who worked at Kodak's laboratories, described a new type of LEDs, organic LEDs (Organic Light Emitting Diodes - OLEDs), so to develop a new type of screen, whose pixels based on OLED. The new screen has excellent features, with much smaller dimensions and lower power consumption. Also, the new type display is able to be constructed on flexible surfaces, such as plastic. This possibility has opened up new prospects for the development of screens. Depending on how the pixel of the display is made (LCD or OLED), there are two possible ways of the pixel driving, which will determine the way of programming: a) driving the pixel with voltage and b) driving with current. Every programming method requires a different design of the peripheral driver circuits of the matrix of the pixels of the screen.

## 2.3 Types of flat displays

The two main types of flat displays are the Liquid Crystal Displays (LCD) and the Organic Light Emitting Displays (OLED), as mentioned in the previous paragraph. Their basic difference has to do with the way the pixels are designed in the screens. While the LC displays are eterofotous, the OLED displays are self-luminous. Subsequently, it will be described the way the liquid crystal display as well as the LED displays are operate and design.

### 2.3.1 *Liquid Crystal Displays – LCD*

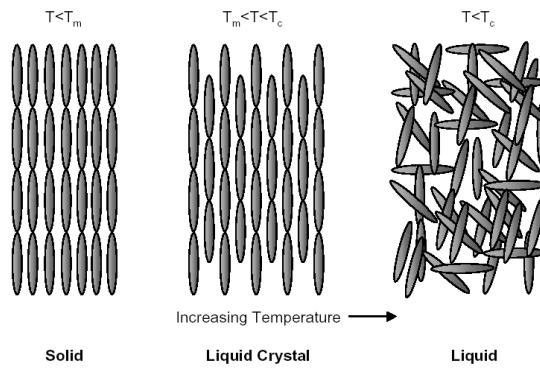

In nature the simple materials are found in three different phases: the crystal, the gas and the liquid. The particularity of the liquid crystals is that they present crystalline properties and properties of the liquid phase at the same time. The

uniqueness of these liquid crystals, is the result of their long molecules and of the oriented layout of their molecular structure. Their unique molecular structure allows the dielectric anisotropy, which are very important for constructing liquid crystal displays. Liquid crystals in the nematic phase are most commonly used in the manufacture of LCDs, because of the physical properties and wide temperature region in which exhibit stability. In the nematic phase, the molecules of the liquid crystals are oriented on average along a particular direction. By applying an electric or magnetic field, the orientation of the molecules can be altered in a controlled manner. This mechanism provides the basis for the operation of LCDs [14].

*Fig. 2.1.: The three states of cholesterol benzoate, depending on temperature*

In 1888, the Austrian botanist Friedrich Reinitzer conducted an experiment with a material known as benzoate cholesterol and observed changes in a solid sample of this material as he was increasing the applied temperature. Specifically, he noted that as the temperature was rising, the solid sample initially became a dull liquid and then turned into a transparent liquid. The physics professor Otto Lehmann, who had learned of the Reinitzer's discovery, conducted its own investigation to confirm that this substance appeared to have two separate melting points,  $T_m$  and  $T_c$ , as shown in fig. 2.1. He was the researcher who devised the term "liquid crystal". Then, liquid crystals are substances that presents properties of solid and liquid material, so they located in an intermediate state of matter.

In nature, liquid crystals can be found in four different phases depending on the orientation of the molecules in their molecular structure: the smectic A and C, the nematic and the cholesterol. Liquid crystals in the nematic phase are most commonly used in the manufacture of LCDs, because of the physical properties and wide temperature region in which exhibit stability. In the nematic phase, the molecules of the liquid crystals are oriented on average along a particular direction. By applying an electric or magnetic field, the orientation of the molecules can be altered in a controlled manner. This mechanism provides the basis for the operation of LCDs.

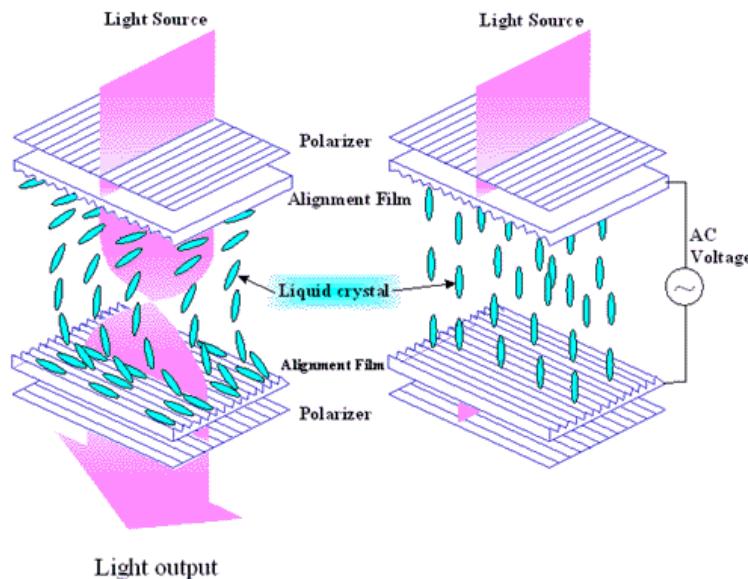

Each pixel cell of an LCD display consists of two glass substrates coated on their inner surfaces with transparent electrodes and separated by a few microns ( $\mu\text{m}$ ) from each other. A nematic liquid crystal material fills the space between the two substrates and two polarizers are attached on both sides of the pixel with their polarization axis crossed.

Figure 2.2.: Principle of operation of a transitional type pixel cell LCD

Externally of two glass substrates, two polarizers are attached on both sides of the pixel with their polarization axis crossed. As shown in fig. 2.2., a nematic liquid crystal material fills the space between the two substrates.

The two glass substrates, each having alignment layer, are oriented with their alignments perpendicular to each other, liquid molecule is twisted initially, as is shown in fig. 2.2. [15].

Also, the light, whose polarity is constantly changing level of polarization due to the swirling liquid crystal, is transmitted through the output polarizer. When a voltage is applied to the electrodes, the director of the molecules tends to orient themselves parallel to the applied field, since liquid crystal materials have positive dielectric anisotropy. Because, in this situation, the polarization of the light transmitted through liquid crystal is crossed to the output polarizer, the light is “cut off” and leaves the cell.

Reflective Technology has a diffuser attached to the rear polarizer. This uniformly reflects incoming light back out through the screen. Because to operate these displays require ambient light, cannot operate in an environment with dim light. These screens usually find application in pocket calculators and digital watches.

The transitional technology has a light source attached to the rear polarizer. So instead of reflecting ambient light, there is a light source within the screen. Most transitional screen technology operate with negative colors, which means that the representation of a character, the character is bright and the background is dark. The transitional technology LCDs have high image quality indoors, but is illegible in natural sunlight. This is due to the intensity of the solar light reflected on the front surface of the LCD, which is much greater than the intensity of light coming from the back of the screen. These screens have applications in medical devices, electrical measuring devices and laptops.

### ***2.3.2 Organic Light-Emitting Display – OLED***

The last decades have seen a rapid development of Organic Light Emitting Diodes, due to the characteristics they have. The great advantage of presenting the OLED displays is the fact that once flowed from electricity, glowing and emitting

light depends on the intensity of the current flowing through them. Furthermore, they present better brightness and contrast ratio compared with LCD screens [16].

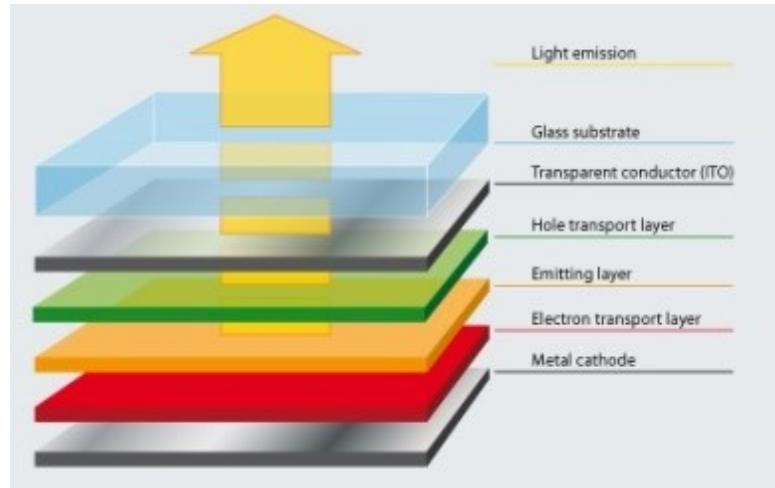

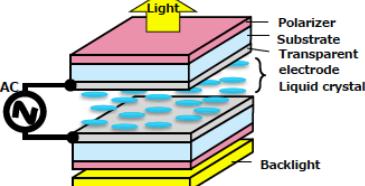

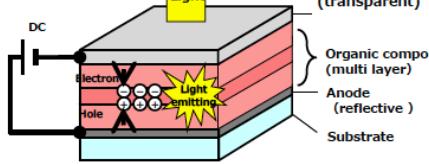

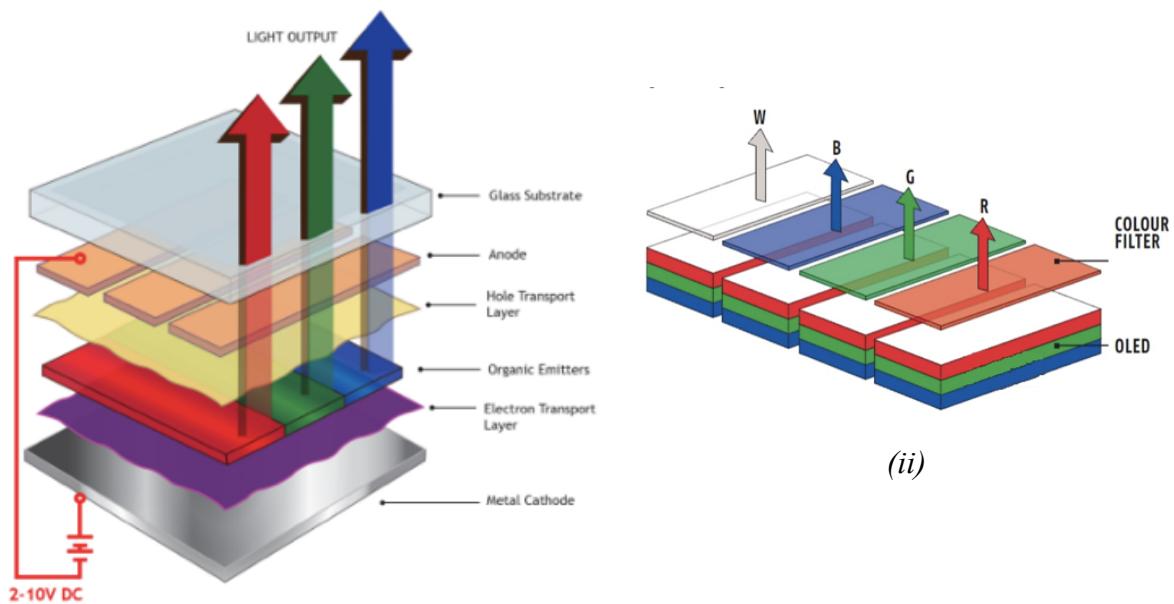

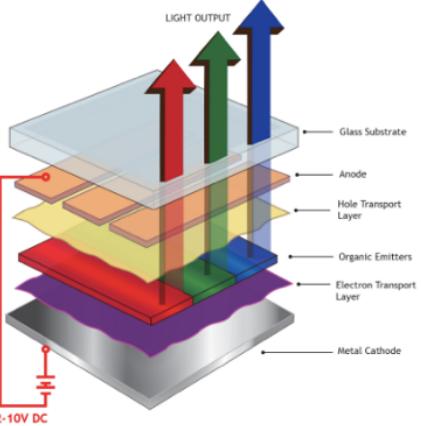

Due to the fact that they do not need a light source, polarizers and diffusers, the construction of the pixel is easier and leads to lower power consumption and many other features. The structure of an OLED is shown in fig. 2.3.

Fig. 2.3.: Structure of an Organic Light-Emitting Display - OLED

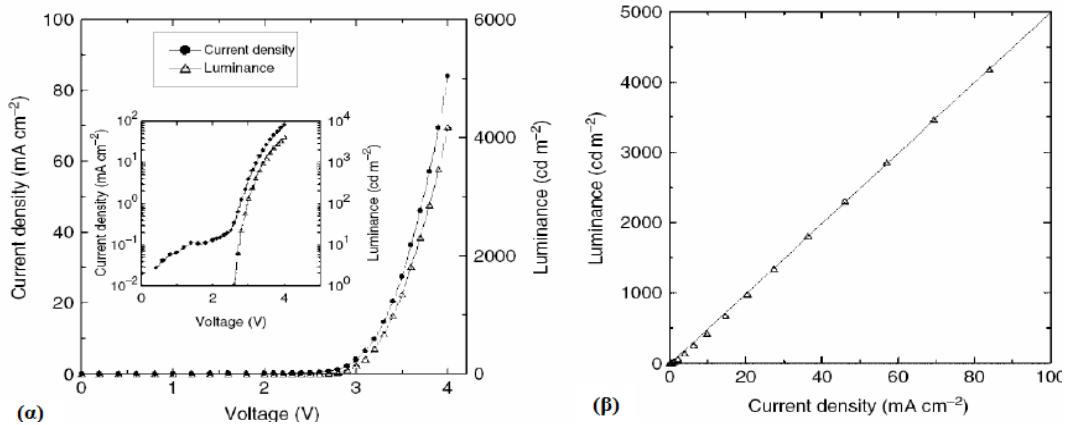

An organic light emitting diode comprises a substrate, which may be glass or other transparent material, and yet flexible, such as plastic. Then, there are two metal electrodes, the anode and the cathode, to which a voltage or current flows through. Between the two electrodes, two organic layers are placed. The first one is a conductive organic layer and the second is also an organic layer, in which, when it's applied voltage or electric current to the electrodes, diffuse carriers (electrons and holes) in this layer, which are recombine and emit light. The color of the emitted light depends on the material of the organic layer. The electrode of the anode must be a transparent material, so as to allow the generated light to emerge from the OLED. This structure has a thickness from 100 to 500 nanometers (nm). Fig 2.4 shows the characteristic curve of an OLED, and the curve showing the brightness of the produced light, compared to the applied electric current [17].

Fig 2.4 (a) Characteristic curve of a photodiode

(b) light produced Brightness as a function of applied electric current.

The characteristic curve of the photodiode resembles the characteristic of a simple diode, with the only difference that the threshold voltage of the photodiode is about 1.5 V, much higher than the threshold voltage of the single-pass. Finally, from the curve of the brightness of the produced light as a function of the applied electric current, we can see that there is a linear relationship between these two sizes.

### 2.3.2a OLED model

The construction and the natural operation of an OLED are the objects of extensive research. However, the characteristics of a photodiode, depend on the manufacturing process and the organic materials which they'll be used. As a result, it is difficult to find a general model that can describes the operation and the characteristics of an OLED device. Moreover, because of requirements of OLEDs market, the research has focused on how to improve the characteristics of OLED, such as lifetime and efficiency, rather than to deeply understand their function and to model them [18].

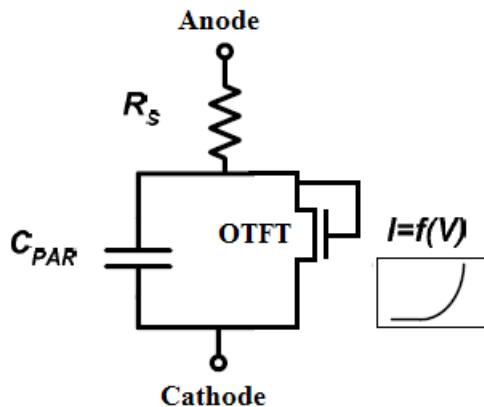

Since there is no standard model for the OLED devices, in the circuit design and pixels, LEDs are considered to be «black boxes» with empirically derived parameters. The equivalent circuit of an organic LED is shown in Fig 2.7.

Fig. 2.7. Equivalent circuit of an organic light emitting diode.

The equivalent circuit consisted of a resistance  $R_s$ , which has a value of about 100 ohms, and a capacitor  $C_{PAR}$ , having a value of about  $25 \text{ nF} / \text{cm}^2$ , depending on the area occupied by the photodiode. Finally, in parallel with the capacitor, a TFT is connected, Diodes, whose geometrical characteristics (length and channel width) depend on the surface occupied by the photodiode, and furthermore has threshold voltage of 1.5 V. This model is generally accepted and it will be used in the simulations of OLED pixels that will follow in the next chapter. The values of the data provided are indicative and exact values depend on each case of the organic materials that will be used and the manufacturing process.

### 2.3.3 Comparison of the displays features

In the table, below, is summarized some of the main characteristics and differences of LCD and OLED displays respectively. Firstly, as is shown there are differences in their structure, as for example the absence of backlight in OLED displays. Also, LCD needs AC voltage while OLED needs DC. Furthermore, the substrate of LCDs is mainly constructed by glass, while in OLED is by glass and film. As for other features of the displays, as is shown, there are differences in power consumption, flexibility and cost.

Table 2: LCD vs OLED

|                      | LCD                                                                                                                                                                                                                                                                                  | OLED                                                                                                                                                                                                                                                                             |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Structure            |  <p>Diagram of LCD structure showing layers: Backlight, Liquid crystal, Transparent electrode, Substrate, Polarizer, and Light exiting. An AC source is connected to the transparent electrode.</p> |  <p>Diagram of OLED structure showing layers: Substrate, Anode (reflective), Organic compo (multi layer), Cathode (transparent), and Light exiting. A DC source is connected to the anode.</p> |

| Substrate            | Glass                                                                                                                                                                                                                                                                                | Glass & Film                                                                                                                                                                                                                                                                     |

| Consumption          | High                                                                                                                                                                                                                                                                                 | Low                                                                                                                                                                                                                                                                              |

| Design<br>“Flexible” | Poor                                                                                                                                                                                                                                                                                 | Excellent                                                                                                                                                                                                                                                                        |

| Cost                 | Low                                                                                                                                                                                                                                                                                  | Fair                                                                                                                                                                                                                                                                             |

## 2.4 Addressing Methods of Flat Display

The addressing methods in the display technology have to do with the way the pixel is designed. There are three different addressing methods: the direct method (direct), the passive matrix (PM) and the active matrix (AM). Depending on the information content that the display manages, the addressing method that will be used, can be selected. The choice of the method that will be used is a very important issue, because the peripheral driving circuits of the pixel array depends on this choice.

### 2.4.1 Direct addressing method

The direct addressing method, which was the first used addressing method, can be used when the content of the managed information is very small, as in the

case of the simple alphanumerical displays, such as calculators and watches. According to this method, its segment is directly connected and controlled individually by the peripheral electronics. The segments are arranged in such way so that they can produce the desired icon [19].

In the direct method, the smallest controllable component for the image production is called segment instead of pixel, which will be used in the two other addressing methods.

#### 2.4.2 *Passive matrix addressing method*

The passive matrix addressing method (PM) is used in larger information applications and is a method for reducing the number of input / output lines that is required.

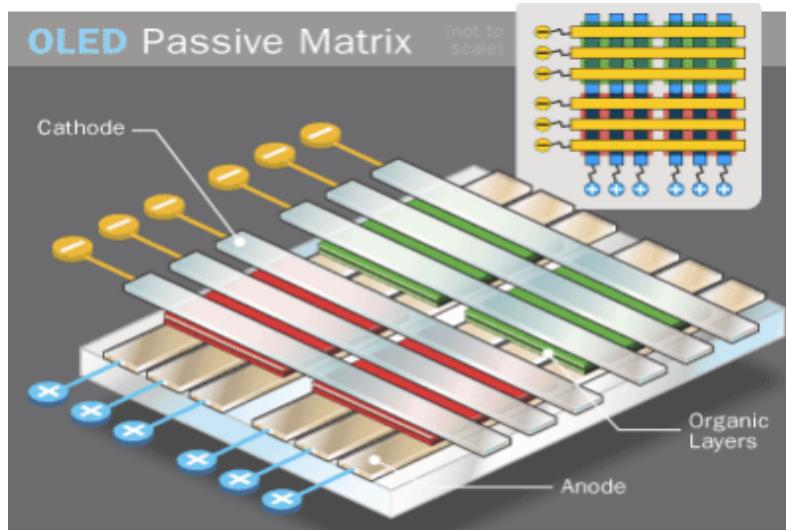

As it is shown in fig. 2.8, PMOLEDs have strips of cathode, organic layers and strips of anode. The anode strips are arranged perpendicular to the cathode strips. The intersections of the cathode and anode make up the pixels where light is emitted. External circuitry applies current to selected strips of anode and cathode, determining which pixels get turned on and which pixels remain off. Again, the brightness of each pixel is proportional to the amount of applied current.

Fig. 2.8. Configuration of the passive matrix addressing method

The passive matrix OLEDs are easy to construct, but they consume more power than other types of OLED, mainly due to the power needed for the external circuitry. PMOLEDs are most efficient for text and icons and are best suited for small screens (2- to 3-inch diagonal) such as screens of cell phones, of PDAs and of MP3 players. Even with the external circuitry, passive matrix OLEDs consume less battery power than the LCDs that currently power these devices. [20]

Furthermore, the disadvantages of the passive matrix method are the low multiplexing capability and the crosstalk effect between the pixels. Crosstalk effect is caused because all the row-pixels are electrically related and a small dc voltage can be added to the pixel voltage from its neighbor pixels. The results of the crosstalk are the poor contrast ratio and the small active region of operation for the displays.

#### ***2.4.3 Active Matrix addressing method***

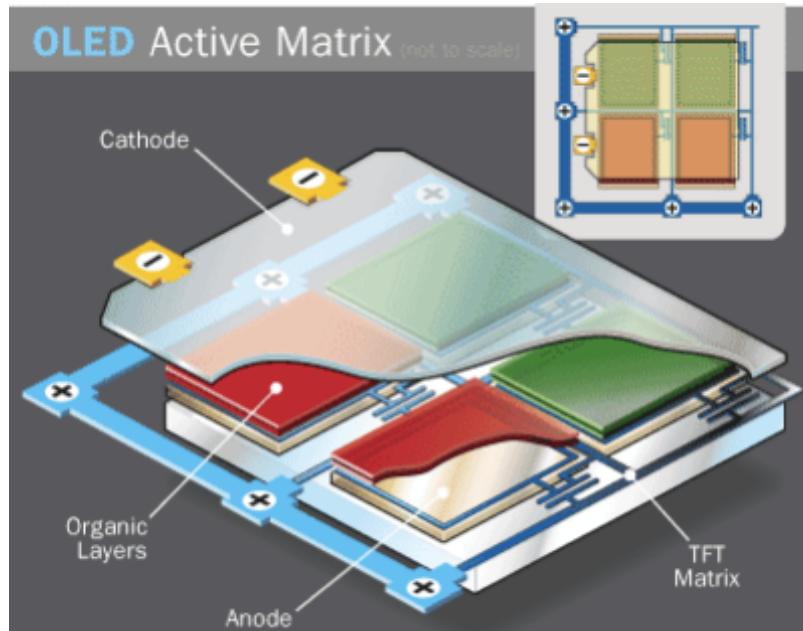

The Active Matrix (AM) addressing method overcomes the multiplexing limitation of the PM method and the crosstalk effect. This can be achieved by incorporating a nonlinear control element, like a switch, in the cross point of the row and column lines (in series connection) of each pixel. The use of a switch will provide a 100 % duty ratio for the pixel by using the charge stored at the pixel during the row addressing time [21].

In Active Matrix, the pixels of the display panel are arranged in x-y axes. Each pixel incorporated into a nonlinear control element (TFT), which functions as an analogue switch and controls the voltage stored in the capacitor of the liquid crystal. The gate pulse of the selected row will turn “ON” the switch TFT of each pixel and simultaneously, the storage capacitor will be charged with the data voltage provided from the column driver. After the row time, the switch TFT will turn “OFF” as soon as the negative edge of the row pulse is delivered and the pixel will be isolated from all its neighbor pixels until the next frame time. This process addressing looks like giving the coordinates (x, y) of the pixel on the panel we want to program so each pixel is independent of the other.

Fig. 2.9. Configuration of the active matrix addressing method.

Fig. 2.9. shows in Active Matrix OLEDs have full layers of cathode, organic molecules and anode, but the anode layer overlays a thin film transistor (TFT) array that forms a matrix. The TFT array itself is the circuitry that determines which pixels get turned on to form an image.

AMOLEDs consume less power than PMOLEDs because the TFT array requires less power than external circuitry, so they are efficient for large displays. AMOLEDs also have faster refresh rates suitable for video. The best uses for AMOLEDs are computer monitors, large-screen TVs and electronic signs or billboards.

## 2.5 The Peripheral Circuit Driving Architecture of Active Matrix Display

In Active Matrix applications, the pixels of the display are programmed by the line-at-a-time method. During one frame, all the Gate Bus rows progressively

scanned with a pulse value  $V_{\text{gate, sel}}$ , while at the same time the Data Bus shows the respective data voltage,  $V_{\text{data}}$ . Suppose that appears on the screen the new image frame. Then, in the first Gate Bus line,  $V_{\text{gate,sel}}$  voltage will be applied, which will force TFT switches of the first line turn to the "ON" state. In all Gate Buses of the remaining rows, the voltage  $V_{\text{g,non-sel}}$  is applied, causing switches of the pixel to be "OFF" state. At the same time, the necessary voltage  $V_{\text{data}}$  applied to the Data Buses. Since, only the pixels of the first row is "ON", only these will be programmed. As soon as even the last pixel of the first row has been programmed, voltage  $V_{\text{g,non-sel}}$  applied to the Gate bus and all its pixels are closing.

### 2.5.1 Architecture of Active Matrix Display

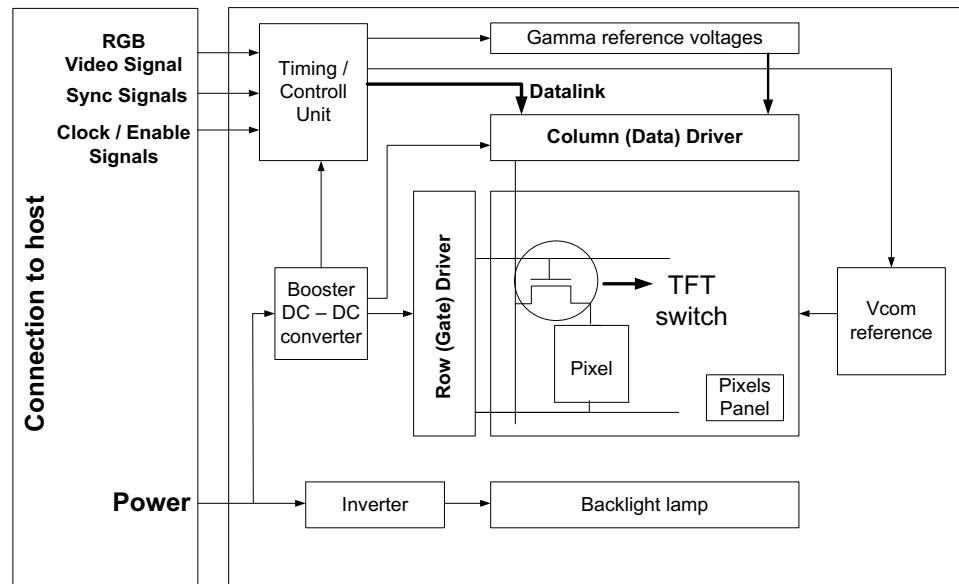

The fig. 2.10, below, shows the Architecture of an Active Matrix screen including the pixels array and the peripheral control and driving circuits of the matrix.

Fig. 2.10. Architecture of Active Matrix Display

The difference between AMLCD and AMOLED display is the absence of the light source (inverter + backlight lamp) on the back of the pixels matrix. The other circuits are similar. Two very important block circuits are those of the timing and control (timing / control unit) and power (booster and DC - DC converter). The timing and control block is basically that, which receives, as input, the video signals (RGB) and translates them into digital signals which are distributed to the other block.

Furthermore, it generates the signals for the clocks of the other block, as well as the synchronization signals of the block together. We can say that the control and timing unit is the "heart" of an Active Matrix screen.

The digital signals of the image are distributed at the column or data driving circuits (column / driver data), and synchronization signals are distributed to row driving circuits or gate (row / driver gate). The row / column peripheral circuits will be described in more detail in the following paragraphs [22].

### **2.5.2 *Gate / Row Driver Circuits***

The row driver block function is the production of line selection signals that controls the synchronization during the programming of rows. Essentially, it produces the signals that are applied to the gates of TFT switches (that each pixel has), and determine if the switch is on "ON" or "OFF" state.

That is why they are often called block and gate drivers. The line selection voltage ( $V_{sel}$ ) must be at least twice bigger than the threshold voltage of the TFT switches to ensure that the switch will operate in saturation area, while the non-selection voltage ( $V_{non-sei}$ ) should be two times smaller than the threshold voltage so that the TFT will be in the cut-off region.

*Fig. 2.11. Architecture of Row / Gate Driver Circuits.*

The duration of the signal line selection pulses is from  $10\mu\text{m}$  to  $70\mu\text{m}$ , depending on the number of lines of the pixels matrix and the duration of the frame. These features are the design specifications of the row driver circuit [23].

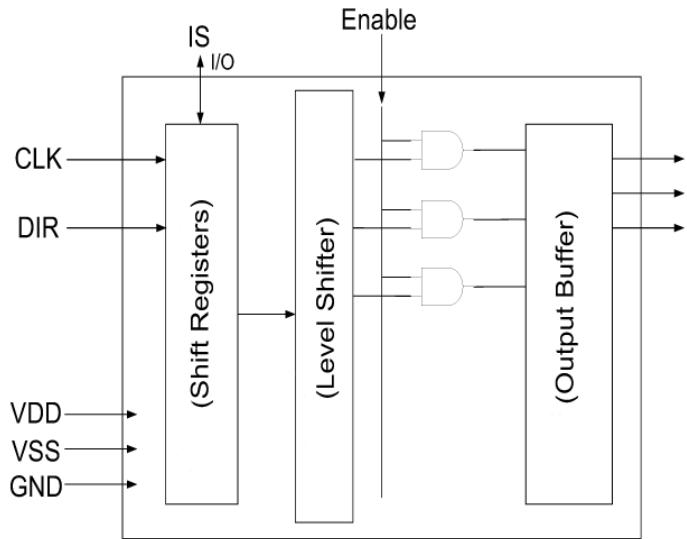

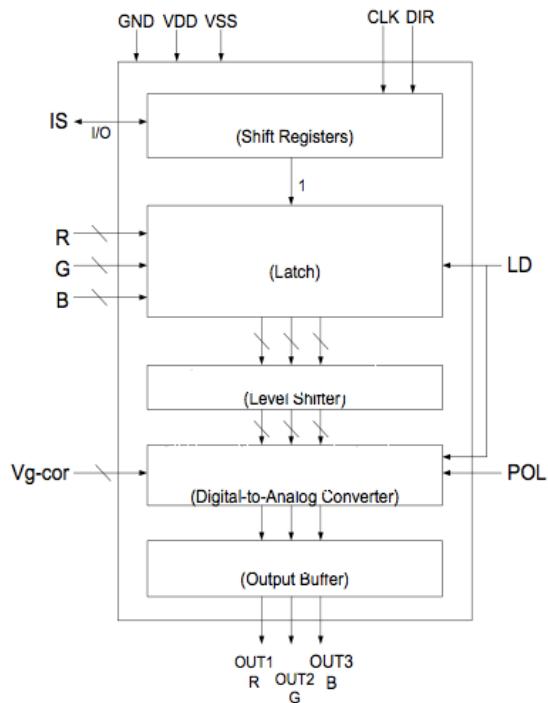

### 2.5.3 **Data/Column Driver Circuits**

The column driving circuit block is more complicated than the row block. The operation of block column driver based on converting the digital image input signal (input digital video signal), into an analog data output signal (output analog data signal) which will be transferred to each pixel. That's why the column driver block often is called data driver block.

The level of the output voltage represents the gray-scale level or of the color that we want for the pixel to emit and it is transferred to the source of the pixel's TFT switch of the same row simultaneously. The brightness emitted by OLED is proportional to the current flowing through Driving TFT. This way, the transformation of  $V_{\text{data}}$  to  $I_{\text{oled}}$  determines the gray-scale.

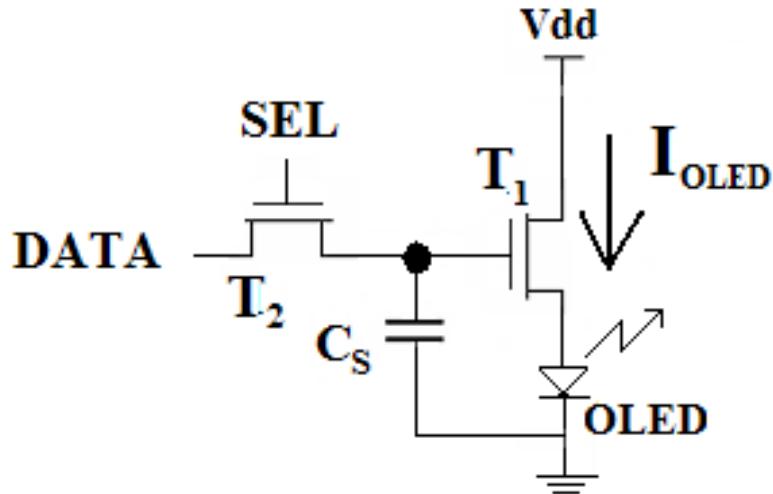

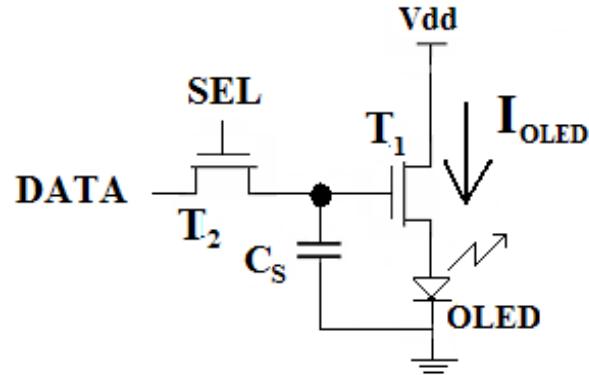

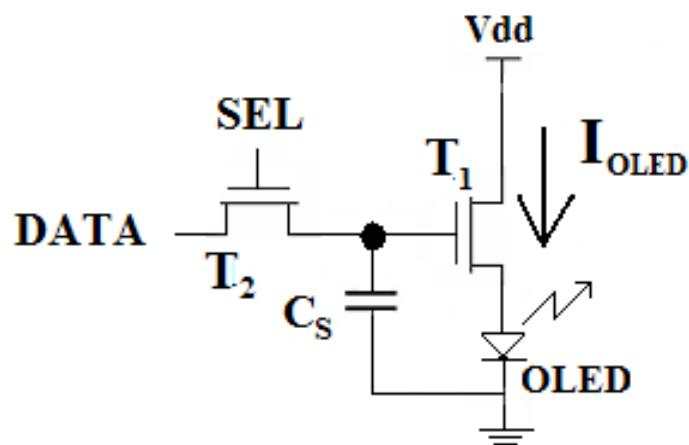

Fig. 2.12. AMOLED pixel, consisted of two TFTs and one storage capacitor  $C_s$  (2T1C)

In both case of LC and OLED pixels, in order to have proper pixels' operation and illumination, the data voltage must be at least about 2 V. This data voltage may reach up to 10 V, depending on the materials used and the number of the gray-scale that the light emitted by the pixel will have. To achieve such an output voltage, the data driving circuits need voltage supply range to 15 V. In special cases, such as large high quality screens, the voltage supply can be as high as 20 V to 25 V. Fig. 2.13 shows the architecture of the data driver block.

A block data driver consists of a bi-directional shift register, which may be implemented in the architecture of multiple successive registers, as in the case of the row driver block. Thus, we achieve scanning the screen from both sides (from right to left or vice versa).

The input start (IS) determined from which side will be the scanning. The digital signals for the three primary colors (red-green-blue) are the *latch input signals*. After the signals are recorded in the latches, they are transferred to the level shifter, to be strengthened and to acquire the necessary voltages values.

Fig 2.13. Architecture of data blocker

Depending on the number of rows and columns, a display has, the video format of the screen is characterized. The ratio of the number of display columns to the corresponding number of rows, is called aspect ratio, while the product of the number of rows and the number of columns is called the resolution of the display. For common screens the aspect ratio is 4:3, while for wide screens, the ratio is 16:9.

Finally, the introduction of new flat panel displays, like Organic Light Emitting Diode (OLED) displays, and the flexible substrate displays have created the need for new TFT technologies, compatible with the new types of flat panel displays.

# **CHAPTER THREE**

# **Organic Light Emitting Diode**

### 3.1 Introduction

The Organic Light Emitting Diodes gave a better solution for the design of the display's pixels for thinner high-performance displays, with lower power consumption. Such displays could be designed with both addressing techniques, active (AMOLED) and passive (PMOLED).

An AMOLED display consists of a certain number of pixels, which are distributed in rows and columns. The total number of pixels of the screen determines its sharpness. The dimensions of a screen is counted by the length of the diagonal, which is usually measured in inches. Also, the ratio of the number of the lines of the pixels to the corresponding number of columns, called ratio of dimensions and is defined for all screens. Formerly the ratio used to be 4:3, but the current wide screens have ratio 16:9.

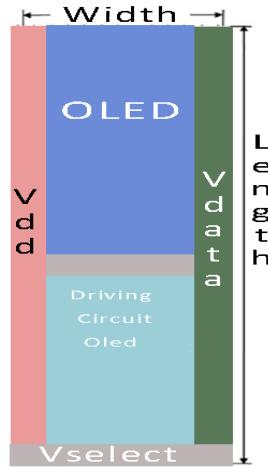

The AMOLED display's Pixels are divided in two parts: The first is the OLED, which illuminate according to the current flowing and the second part is the circuit which generates the necessary current of the OLED, as shown in Fig. 3.1.

The circuit part is not transparent, while only OLED radiates. The ratio of the transparent area (OLED) to the ratio of the non-transparent surface (circuits with lines), called the aperture ratio. Finally, in each pixel there are rows of signals, which is the selection signal from the block line driver, the data signal coming from the block column drivers and the supply voltage.

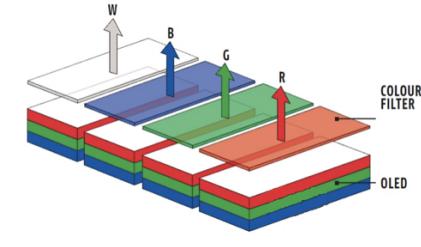

As the objective of the displays is color production. With the appropriate combination of the three primary colors, Red - Green – Blue (RGB), all colors in nature can be created. There are two ways for color generation for OLED displays. First way is with color OLEDs and the other way with only white ones and color filters. Both ways have advantages and disadvantages [24].

Fig. 3.1. Schematic representation of a pixel of an AMOLED display

The first way, is the method of depositing RGB emitting layers at each pixel and it is called the *Shadow Mask Patterning Method*. Since the displays produced by this method have independent emitting layers they have excellent color purity and contrast. Also , it is possible to have high luminance efficiency and low power consumption, because there are no need of RGB color filters to use.

Fig 3.2. i) Color Oled - Shadow Mask Patterning Method, ii) Color Filter Method

Table 3.

Structure of the two different ways of color production - advantages/disadvantages

|                                                                                                                                            | Positives                                                                                                                       | Negatives                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|  <p><i>Color Oled - Shadow Mask Patterning Method</i></p> | <ul style="list-style-type: none"> <li>• High color purity</li> <li>• High Contrast</li> <li>• Low power consumption</li> </ul> | <ul style="list-style-type: none"> <li>• High accuracy for deposition Required</li> <li>• Various lifetime lengths depending on each pixel</li> </ul> |

|  <p><i>Color Filter Method</i></p>                      | <ul style="list-style-type: none"> <li>• Simple production</li> <li>• No difference lifetime</li> </ul>                         | <ul style="list-style-type: none"> <li>• High energy loss</li> <li>• High power consumption</li> </ul>                                                |

The second way, is the method which produce colors through the use of RGB color filter and it is called *Color Filter Method*. With this method, the OLED materials, including RGB color elements, produce white light which is then filtered to obtain the desired colors. It is not necessary to have a wide variety of OLED materials so only one kind of OLED material is used to produce white light. Some disadvantages are low color purity and contrast. Also, the filters used with the method absorb most of the light energy emitted, requiring the white light to be relatively strong. Therefore, power consumption for the displays produced by this method is higher. Both mono-color panels and full-color panels have these

characteristics. The two figures in fig. 3.2 show the structure of the two different ways of color production.

Table 3 shows the structure of the two different ways of color production, as well the advantages and the disadvantages of the two ways of color production.

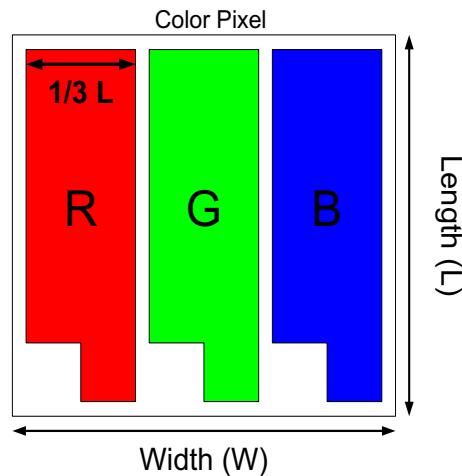

In order each pixel can illuminate all colors, it is divided into three sub-pixels, each of which illuminates a base color. As the pixel has a square shape, the width of each sub-pixel is the  $1/3$  of its length, as it is shown in fig. 3.3. Each color is created by the light intensity produced by the OLED, which it is determined by the current flowing through it.

The circuit of the pixel can be implemented by various thin-film transistor technologies. The two main technologies used by the industry, are amorphous silicon transistors (a-Si TFTs) and polycrystalline silicon (pc - Si TFTs).

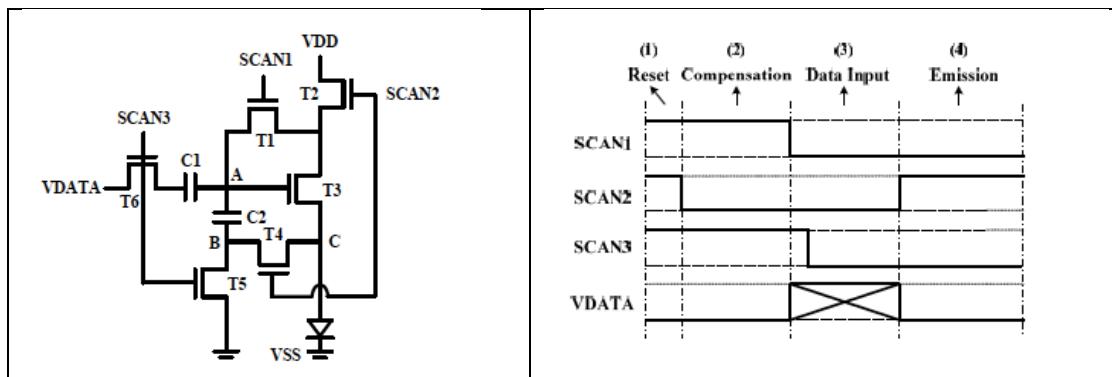

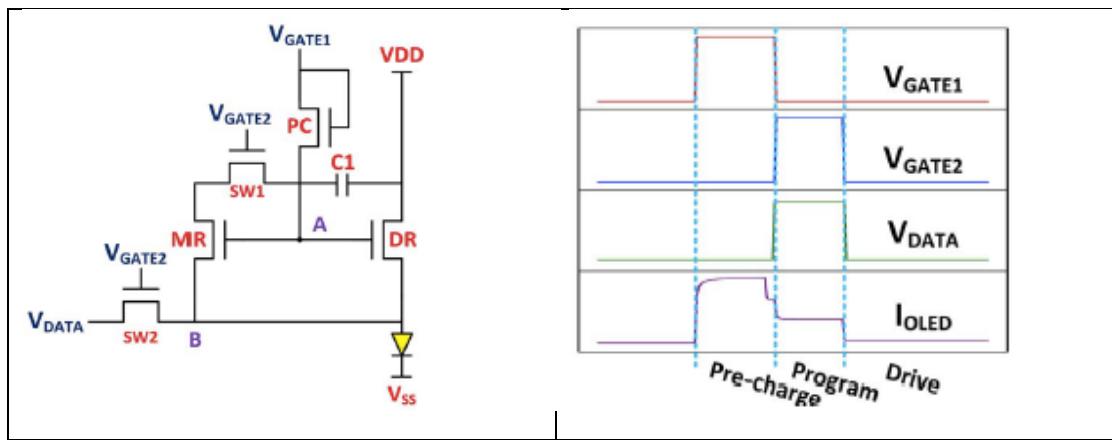

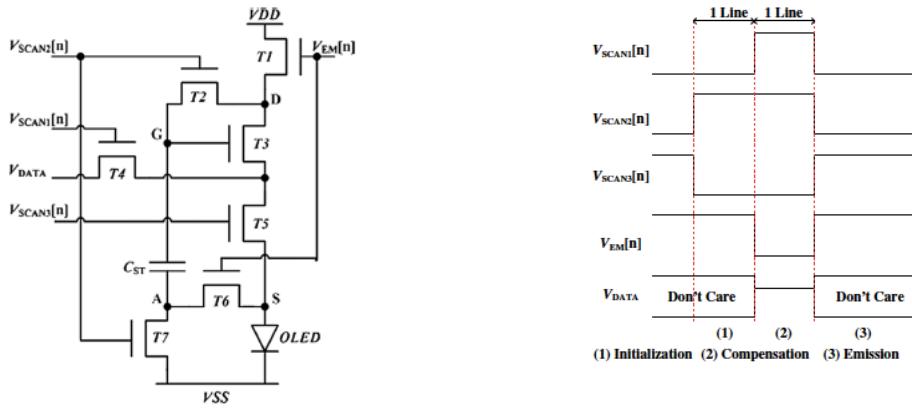

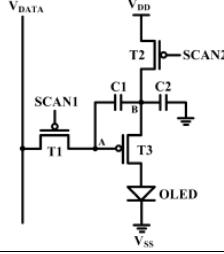

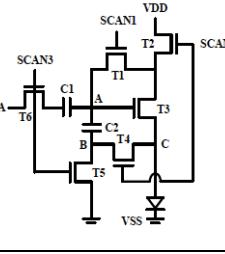

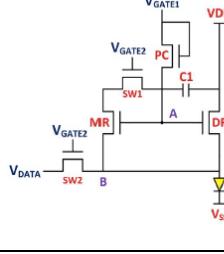

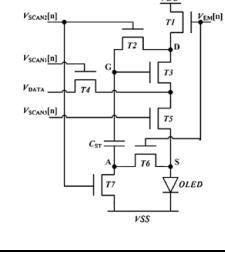

Fig. 3.3: Typical full color square pixel